## New Strategies for Engineering Tensile Strained Si Layers for Novel n-Type MOSFET

Thomas David, Isabelle Berbezier, Jean-Noël Aqua, Marco Abbarchi, Antoine Ronda, Nicolas Pons, Francis Domart, Pascal Costaganna, Gregory Uren, Luc Favre

### ► To cite this version:

Thomas David, Isabelle Berbezier, Jean-Noël Aqua, Marco Abbarchi, Antoine Ronda, et al.. New Strategies for Engineering Tensile Strained Si Layers for Novel n-Type MOSFET. ACS Applied Materials & Interfaces, 2021, 13 (1), pp.1807-1817. 10.1021/acsami.0c16563 . hal-03111073

## HAL Id: hal-03111073 https://amu.hal.science/hal-03111073v1

Submitted on 15 Jan 2021

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# New strategies for engineering tensile strained Si layers for novel N-type MOSFET

Thomas David<sup>a,b</sup>, Isabelle Berbezier<sup>c\*</sup>, Jean-Noël Aqua<sup>d</sup>, Marco Abbarchi<sup>c</sup>, Antoine Ronda<sup>c</sup>, Nicolas Pons<sup>a</sup>, Francis Domart<sup>a</sup>, Pascal Costaganna<sup>a</sup>, Gregory Uren<sup>a</sup>, Luc Favre<sup>c\*</sup>

<sup>a</sup> XFAB, 91100 Corbeil Essone, France

<sup>b</sup> present address: CEA-LITEN, 38000 Grenoble, France

<sup>d</sup> INSP, CNRS, Sorbonne Uni., 75252 PARIS Cedex 05, France

#### Abstract

We report a novel approach for engineering tensely strained Si layers on a relaxed Silicon Germanium On Insulator (SGOI) film using a combination of condensation, annealing and epitaxy in selected conditions well chosen based on elastic simulations. The study evidences the remarkable role of SiO<sub>2</sub> buried oxide layer (BOX) on the elastic behavior of the system. We show that tensely strained Si can be engineered by using alternatively rigidity (at low temperature) and viscoelasticity (at high temperature) of the SiO<sub>2</sub> substrate. In these conditions, we get a Si strained layer perfectly flat and free of defects on top of relaxed  $Si_{1-x}Ge_x$ . We found very specific annealing conditions to relax SGOI while keeping an homogeneous Ge concentration and an excellent thickness uniformity resulting from the viscoelasticity of SiO<sub>2</sub> at this temperature, which would allow layer by layer matter redistribution. Remarkably, Si layer epitaxially grown on relaxed SGOI remains fully strained with -0.85 % tensile strain. The absence of strain sharing (between Si<sub>1-x</sub>Ge<sub>x</sub> and Si) is explained by the rigidity of the Si<sub>1-x</sub>Ge<sub>x</sub>/BOX interface at low temperature. Elastic simulations of the real system show that, due to the very specific elastic characteristics of SiO<sub>2</sub>, there are unique experimental conditions that both relax  $Si_{1-x}Ge_x$  and keep Si strained. Various epitaxial processes could be revisited in the light of these new results. The generic and simple process implemented here meets all the requirements of the microelectronics industry and should be rapidly integrated in the fabrication lines of large multifinger 2.5 V n-type MOSFET on SOI used for RF-switches applications and for many other applications. Keywords: strained silicon, epitaxy, relaxation, condensation, MOSFET, carrier mobility,

<sup>&</sup>lt;sup>c</sup> Aix Marseille Univ, CNRS, Université de Toulon, IM2NP, 13397 Marseille CEDEX 20, France

#### 1. Introduction

Strain engineering has long been an active area of development to enhance the key characteristics of Si MOS devices. There have been generally two different approaches. The first is a global or wafer scale pursued by IBM and then at Bell Labs to create a  $Si_{1-x}Ge_x$  template from which a strained layer could be formed. As a consequence of the lattice misfit, defect management and complexity were difficult challenges to overcome. Industrialization was not realized. On the other hand, alternative approaches for planar MOS architectures included a tensile strained contact etch stop layer for NMOS. For PMOS, the substitution of Si with strained Si<sub>1-x</sub>Ge<sub>x</sub> alloys within the source/drain regions has been widely adopted. Within the era of digital scaling, the minimum devices are extensively used to construct the basic building blocks of digital design. The aforementioned approaches are most effective with minimum geometries. Challenging notwithstanding, the wafer scale engineering retains the advantage that the benefit of the mobility enhancement can also be realized also with longer channel lengths (>150 nm). In one particular application of interest and the motivation for this study, RF switches constructed of cascaded NMOS in RF-SOI technologies could benefit from a reduction of the on-state resistance without significant compromise of power handling. The commonly used figure of merit for RF Switches is Ron  $\times$  Coff (fs). Ron ( $\Omega$ ) is an indicator of the insertion loss of the RF signal between the antenna and the desired port and Coff (fF) is an indicator of the isolation between antenna and undesired ports. Both have to be as low as possible. The Ron is mainly limited by the channel resistance, thus one way to reduce it is to decrease the Gate length, but this approach is limited because the device has to sustain high power especially in OFF-state. The process developed in this study aims at highly improving the mobility whatever the channel length, and thus decreasing the Ron accordingly.

Tensile strained silicon has been proposed for more than twenty years as a booster of silicon-based CMOS transistors to improve the performance of very large scale integrated (VLSI) circuits independent of device geometry and scaling. It has been experimentally demonstrated that the effective electron mobility in MOS structures can be significantly enhanced using tensile strained-Si channel grown on Si<sub>1-x</sub>Ge<sub>x</sub> relaxed buffer layer with an increase of Ion/Ioff ratio and more than 50 % transconductance enhancement in short-channel n-MOSFETs [1]; [2]; [3]; [4]; [5]; [6]; [7]; [8]. n-channel with mobility 75 % higher than in coprocessed bulk Si devices were reported, demonstrating that the mobility enhancement in strained-Si inversion layers was independent of vertical electric field. Furthermore, it was shown that the enhancement in carrier mobility observed at low lateral field did translate into improved performance at high lateral field [9]. In parallel, various theoretical calculations

also predicted an enhancement of the drive current and then of the speed [10] [11] [12]. The strain of the Si layer was shown to cause an increase in the electron mobility (up to factors of 1.5 and 1.9 for x = 10 % and 20 % respectively), over the entire range of transverse electric field ( $E_{\perp}$ ).

Among the first works dedicated to strained silicon, [13] aimed at the fabrication of two-dimensional electron gas (2DGs) consisting of a strained Si well sandwiched between two  $Si_{1-x}Ge_x$  relaxed layers and taking advantage of the 4.2 % misfit between Si and Ge crystalline lattice. Higher electron mobility was assumed to originate from changes in the band structure with carrier confinement in the Si layer. The biaxial tensile strain introduces splitting of degenerate bands, which results in smaller in-plane conduction mass and reduced intervalley scattering thereby yielding improved carrier velocity [14]. While an optimization of the structures could be achieved with an increase of the space thickness and lowering the carrier concentration and the background impurities, the main bottlenecks to be raised concern the large density of threading dislocations throughout the whole structure.

Most of the work carried out in the 2000s has been completed on  $Si_{1-x}Ge_x$  relaxed substrate, trying to decrease the density of dislocations in the buffer and optimizing the associated surface roughness [15]; [16]; [17]; [18]; [19]; [20]. When the low-defect density  $Si_{1-x}Ge_x$  relaxed buffers have been integrated into FETs, they have demonstrated high electron mobility in strained-Si and high hole mobility in strained-Ge (and Ge-rich alloys). *n*-MOSFET which have a simple epitaxial structure and require low Ge concentrations in  $Si_{1-x}Ge_x$  relaxed buffer layers, represent the devices for which improvements of performances in short-channel devices are most important and best documented, with robust mobility and significant transconductance enhancements demonstrated on large scales [21]. The incorporation of a  $Si_{1-x}Ge_x$  layer with a high Ge content was also shown to minimize the overall strain within the device and to produce optimized strained-Si/Si\_{1-x}Ge\_x channel with even higher electrical performance in terms of transconductance, field-effect mobility and on-state drain current enhanced by up to 170 % while excellent off-state leakage currents and subthreshold characteristics [22]; [23]. This result was obtained without Chemical-Mechanical Polishing (CMP) step of the surface, while it is well-known that such process step is critical for transistor properties reliability [21].

Despite all the promising results obtained in research groups, so far, no technology based on strainedsilicon could be transferred to production due to the unreliability of the process induced by the formation of misfit dislocations during the various subsequent steps of the process. In fact, published drive current I<sub>on</sub> enhancements are at most 15 % – 20 % for L<sub>gate</sub>  $\approx$  100 nm. Then more attention should be devoted to the optimization of several parameters besides mobility and CMOS process for strainedSi. So far, the various approaches under progress produce considerable variations in device performances. While the quality of the strained-Si epitaxial layer is usually directly linked to the underlying Si<sub>1-x</sub>Ge<sub>x</sub> relaxed buffer layer (threading and misfit dislocations density and surface morphology), in manufacturing, many other criteria have to be checked, for example uniformity of Ge-content and Si thickness to ensure consistent transistor performances on large scale wafers. But also, the level of Ge content in the Si<sub>1-x</sub>Ge<sub>x</sub> virtual substrate which is decisive for the electron mobility of *n*-MOSFET, since it sets the amount of strain-induced splitting between the  $\Delta 2$  and  $\Delta 4$  valleys in the Si layer.

It is therefore essential to study in detail the influence of the different conceptual parameters of the system under consideration. As regards Ge content, in some studies it was reported that the mobility monotonically increases with strain up to  $x \approx 0.2$  (strain 0.8 %) and then saturates. This is because at this strain level, the conduction-band splitting is sufficient to completely suppress intervalley phonon scattering, and thus only little enhancement of electron mobility could be gained at higher strain [24]. In other studies, an enhancement of the electron mobility by  $\approx 120$  % was measured for x  $\approx 0.30$ , despite the large misfit (between Si and  $Si_{1-x}Ge_x$ ) causing high density dislocations. Monte Carlo simulations attributed these discrepancies to additional electron mobility-limiting mechanism such as defect scattering (surface roughness and high density of defects) in the epitaxial strained-Si/Si<sub>1-x</sub>Ge<sub>x</sub> system [25]. Simulations results were confirmed by the comparison of mobilities measured on systems before and after CMP. It was shown that CMP eventually followed by epitaxy of thick silicon, significantly improves mobilities, when compared to devices without CMP [21]. The thickness of the strained Si layer has also a strong influence: under low effective field, as this thickness decreases, the number of electrons in the Si<sub>1-x</sub>Ge<sub>x</sub> and close to the SiO<sub>2</sub>/Si interface increases, creating parasitic conduction and scattering events that degrade the overall mobility. Under high effective fields, the electrons are all located in the strained Si layer and the Si thickness has no influence on the mobility. For NMOS devices the Si thickness should then be larger than  $\approx 10 \text{ nm}$  [26].

More recently, the combination of tensile strained silicon with  $Si_{1-x}Ge_x$  on insulator (SGOI) has been proven to offer new opportunities to increase the devices performances. New efforts were made to transfer the advantages obtained in bulk CMOS technology to insulating substrate [27]; [28]; [29]; [30]; [31]; [32]; [33]. However, the measured values of ohmic mobilities that can be as high as 53105  $cm^2V^{-1}s^{-1}$  at low temperature, were shown to strongly depend on the interface roughness and on the material quality. In general, the mobility characteristics of n-MOSFETs fabricated on strained-Si layers transferred to insulating handle wafers has been found to be nearly identical to those on  $Si_{1-x}Ge_x$  graded buffers. The main reason for this is that generally, the fabrication process of the strained-Si/Si<sub>1-x</sub>Ge<sub>x</sub> relaxed buffer layer remains the same, while only a transfer step of  $Si_{1-x}Ge_x$  on SOI is added. Indeed, the tensile strained Si in the channel on BOX has been generally implemented following only two ways: 1) making strained Si/relaxed  $Si_{1-x}Ge_x$  on buried oxides using layer exfoliation to transfer the relaxed  $Si_{1-x}Ge_x$  buffer on SOI; 2) bonding and transfer the strained Si layer directly on the BOX. Another method using SIMOX process was suggested but it is limited to  $x \le 0.1$  which is then not useful for most of the microelectronic applications.

In this work based on elastic simulations we show that tensile strained Si can be engineered by alternatively using rigidity (at low temperature) and viscoelasticity (at high temperature) of the Si<sub>1-x</sub>Ge<sub>x</sub>/SiO<sub>2</sub> interface. We then demonstrate both theoretically and experimentally an original and simplified process that should be easily integrated in NMOS device for the fabrication of tensile strained Si layer. We show that using a combination of epitaxy and condensation steps in very specific experimental conditions (i.e. low temperature  $Si_{1-x}Ge_x$  condensation and high temperature annealing) we can get strained Si layer perfectly flat and free of defects on top of relaxed Si<sub>1-x</sub>Ge<sub>x</sub>. In very specific annealing conditions Si<sub>1-x</sub>Ge<sub>x</sub> layer (on BOX) is relaxed, while keeping an homogeneous Ge concentration (x  $\approx$  20 %) and an excellent thickness uniformity. This results from the viscoelasticity of SiO<sub>2</sub> at this temperature, which could allow layer by layer matter redistribution. Cross-section High Resolution Transmission Electron Microscopy (HRTEM) images highlight the very flat surface/interface and the absence of extended defects. Another very interesting result is that the Si layer grown on top of this relaxed Si<sub>1-x</sub>Ge<sub>x</sub> remains fully strained with - 0.85 % tensile strain measured in the layer, by both geometrical phase analyses (GPA) of HRTEM images and interatomic lattice plane distance measurements. The absence of strain sharing (between  $Si_{1-x}Ge_x$  and Si) is explained by the rigidity of the Si<sub>1-x</sub>Ge<sub>x</sub>/BOX interface at low temperature (Si epitaxy at 500 °C). In more detail, the elastic nonlinear simulations of the real system in our experimental conditions show that for Si<sub>1-x</sub>Ge<sub>x</sub> (x = 0.2, e = 19 nm) the maximum thickness up to which there is no relaxation of the Si top layer is 83 nm.

Due to very specific elastic characteristics of  $SiO_2$ , we have found unique experimental conditions that both relax  $Si_{1-x}Ge_x$  and keep Si strained. The generic process implemented here can be easily integrated in the fabrication lines of large multifinger 2.5 V n-type MOSFET on SOI used for RF-switches applications and meets all the requirements of the microelectronics industry for many other applications. The generic behavior found could be applied to many other heteroepitaxial systems.

#### 2. Materials and methods

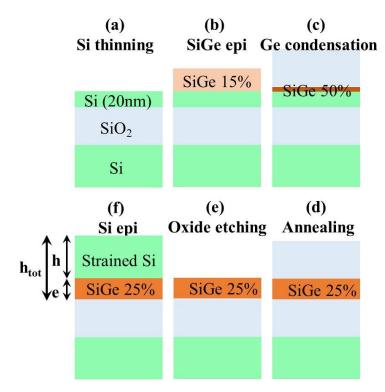

The process for the fabrication of tensile strained Si layer is schematically illustrated in Figure 1. The investigated SOI wafers are commercially available from SEH. The investigated structures were fabricated in state of the art 200 mm technology semiconductor facility of XFAB France. They initially consist of a 140 nm thick top-Si layer on top of 400 nm thick BOX (Figure 1a). The function of the poly-Si layer under the BOX is to suppress harmonic generation primarily from the active devices and to improve the linearity of RF switch devices. It is commonly referred to as a "trap-rich" layer. The 400 nm-thick BOX consolidates this effect and also provides isolation between back side and front side. The top Si layer is first locally thinned using LOCOS process followed by a wet etch to reach 20 nm. Thickness uniformity and surface flatness are systematically controlled over the entire wafer by ellipsometry. A thickness inhomogeneity lower than 8 % over the whole 8" wafer was found. At first, 20 nm Si<sub>1-x</sub>Ge<sub>x</sub> film with x = 0.15 is epitaxially grown by Solid Source Molecular Beam Epitaxy (MBE) in a 200 mm UHV growth chamber (SG800 model from DCA Instruments) after ex situ chemical cleaning and in situ thermal cleaning (Figure 1b) that consist of chemical oxidation (2 to 8 min HF etching) and thermal annealing (at 500 °C for 10 min) steps respectively. Si and Ge fluxes are produced with solid sources using e-beam evaporator and effusion Knudsen cell for Si and Ge respectively. The growth rates are monitored in situ by RHEED. Si and Ge growth rates are 1 nm min<sup>-</sup> <sup>1</sup> and 0.1 nm min<sup>-1</sup> respectively. The growth temperature is set at 400 °C for both Si<sub>1-x</sub>Ge<sub>x</sub> and Si.

Next, thermal oxidation in O<sub>2</sub> atmosphere is carried out in a Rapid Thermal Oxidation (RTO) furnace at low temperature (typically 750 °C). During this step the selective oxidation of only Si atoms, leads to the formation of SiO<sub>2</sub> on the top of the structure and to the repulsion of Ge atoms underneath the SiO<sub>2</sub>, resulting in a pile-up of Ge at the SiO<sub>2</sub>/Si<sub>1-x</sub>Ge<sub>x</sub> interface (Figure 1c). Oxidation is carried out during 70 min to obtain a 10 nm thick Si<sub>1-x</sub>Ge<sub>x</sub> layer with a Ge concentration about 50 %. The wafer is then furnace annealed (Rapid Thermal Annealing) under inert nitrogen atmosphere. RTA of these samples were done at various temperatures and N<sub>2</sub> pressures. This treatment promotes the interdiffusion between Si and Si<sub>1-x</sub>Ge<sub>x</sub> and leads to the homogenization of Ge concentration across the Si<sub>1-x</sub>Ge<sub>x</sub>/Si heterostructure (Figure 1d). As a result, Si<sub>1-x</sub>Ge<sub>x</sub> and Si layers mix to form a homogeneous Si<sub>1-x</sub>Ge<sub>x</sub> layer with a lower fraction of Ge and a total thickness thinner than the initial (Si<sub>1-x</sub>Ge<sub>x</sub> + Si) one. Small thickness is a key parameter to favor strain relaxation by gliding and redistribution of matter at the interface (see discussion). In addition, since the total amount of Ge in the SGOI layer is preserved throughout the process, the final Ge concentration in SGOI can be easily estimated ahead of time. Condensation time is then fitted to obtain a final SGOI concentration of  $x \sim 0.25$  that is enough to efficiently stress the silicon top layer. It also has a sufficiently low thickness (< 20 nm) to avoid nucleation of dislocation and facilitate elastic strain relaxation (see simulations part) during the annealing step.

The last crucial step is the re-epitaxy of silicon. This is done after chemical etching of SiO<sub>2</sub>, i.e. by dipping the sample in a HF diluted solution (Figure 1e). A film of 70 nm Si is epitaxially grown in MBE at low temperature typically 500 °C (Figure 1f).

Figure 1: Process flow diagram: (a) Nominal substrate after Si thinning; (b) Si<sub>1-x</sub>Ge<sub>x</sub> epitaxy; (c) Ge condensation during RTO; (d) Furnace annealing for homogenization (950 °C); (e) Chemical etching of oxide; (f) Si epitaxy

The industrial developments require accurate and reliable metrology methods for the characterization and subsequent control of the magnitude of strain (relaxation) in the s-Si layer (Si<sub>1-x</sub>Ge<sub>x</sub> buffer) and the Ge content (x). To this end, Transmission Electron Microscopy (TEM), Energy Dispersive Spectroscopy (EDS) and Geometrical Phase Analysis (GPA) are the only analyses that give simultaneously and locally these parameters. Thickness and crystal quality of the SGOI layer were assessed by cross-section TEM. TEM specimens were prepared by Focused Ion Beam (FIB) milling using a dual-beam FEI Helios 600 NanoLab. The strain distribution throughout the films is imaged and mapped using GPA. High Resolution-TEM observations were performed using a Microscope MET FEI Titan 80-300 with Cs corrector operating at 300 keV. Transmission Electron Microscopy (TEM), Scanning Transmission Electron Microscopy and High-Angle Annular Dark-Field imaging (STEM HAADF) and Energy-Dispersive X-ray Spectroscopy (EDS) were done using a FEI Tecnai G2. Most of the strain values are given relatively to the reference (unstrained Si lattice from the substrate under the BOX). When the BOX is too thick, the reference is taken in the Si<sub>1-x</sub>Ge<sub>x</sub> layer whom Ge composition is estimated by EDS. More generally EDS using GATAN semi-quantitative analyses is used to estimate the Ge concentration throughout the films after the various fabrication stages.

#### 3. Results and discussion

#### 3.1 Strain determination

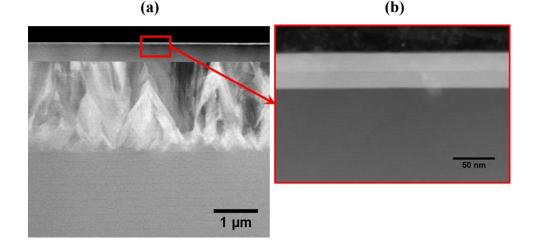

We start the process by the epitaxy of a  $Si_{1-x}Ge_x$  film with a low Ge concentration (x = 0.15) to avoid the formation of dislocation during the various fabrication stages. Epitaxial  $Si_{1-x}Ge_x$  layers with x  $\geq$ 25 % could not be used because of the formation of dislocation during the process. Figure 2 gives a cross-section overview of the whole system including Si(001) substrate, poly-silicon, 400 nm thick BOX and Si<sub>1-x</sub>Ge<sub>x</sub>/Si top layers. The STEM HAADF (Figure 2a) highlights the dislocations and extended defects in thick polysilicon underneath the BOX. The quality of the epitaxy and the absence of defects can be assessed on Figure 2b which gives a magnified view of the Si/Si<sub>1-x</sub>Ge<sub>x</sub> epitaxy.

Figure 2: STEM HAADF cross-section images of: (a) the whole structure; (b) The Si/Si<sub>1-x</sub>Ge<sub>x</sub> epitaxy.

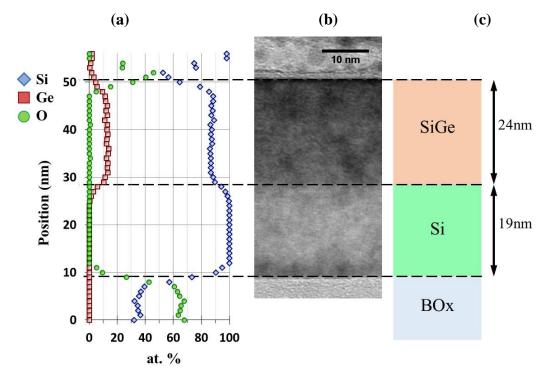

The semi-quantitative analysis of the layer composition is made by EDS (Figure 3a). The elemental depth analyses profiles of Si, Ge and O highlight the uniformity of the Ge composition across the layer and the abruptness of the Si<sub>1-x</sub>Ge<sub>x</sub>/SOI interface resulting from the L.T. MBE growth process (T = 500 °C). The layers thickness and composition can also be deduced from the line profiles. Both the thickness (20 nm and 24 nm measured for Si and Si<sub>1-x</sub>Ge<sub>x</sub> respectively) and the Ge concentration (x = 0.15) perfectly fit with the nominal parameters. The corresponding diagram summarizes the starting structure (Figure 3c).

Figure 3: (a) EDS line profile of the elemental composition of the layers; (b) TEM diffraction contrast; (c) Diagram of the structure with the deduced thickness.

Condensation is commonly carried out during dry thermal oxidation at high temperature (H.T.) typically between 1000 °C and 1200 °C. However, during H.T. oxidation, dislocations nucleation is easily promoted [34]; [35]; [36] together with the buckling of  $Si_{1-x}Ge_x$  layers due to the viscous flow of oxides surrounding the  $Si_{1-x}Ge_x$  layers [37]. We reported recently, that fully strained and free of

dislocations Ge rich layers (GRL) with flat surface and abrupt interface, can be fabricated using low temperature condensation [38]; [39]. In these experimental conditions, the basic mechanism of GRL formation is a self-limited interdiffusion process regulated by the entropic term of the formation energy which is minimum at  $Si_{0.5}Ge_{0.5}$  at the expense of the elasticity driven interdiffusion. The process developed provides an easy and efficient way to produce planar GRLs with remarkable elastic features. It also enables the total inhibition of the morphological instability (which commonly develops during the growth of  $Si_{1-x}Ge_x$  on Si [40]; [41]), together with the hindering of dislocations for critical thickness much larger than the ones commonly obtained by direct deposition. Those behaviours were explained by the injection of self-interstitials in the GRL during condensation.

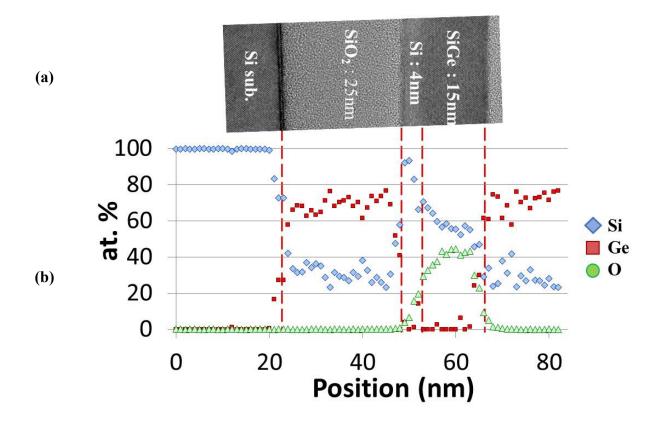

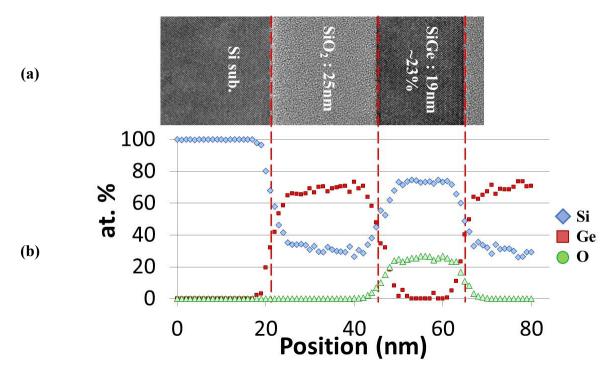

The present process takes advantage of this fabrication of GRLs, fashioning them for the fabrication of relaxed Si<sub>1-x</sub>Ge<sub>x</sub> template layers with lower Ge concentration, best suited to the device targeted here. The first condensation tests were performed at 800 °C using a test sample constituted of 25 nm BOX and 19 nm Si<sub>1-x</sub>Ge<sub>x</sub>/SOI. The reduced thickness of the BOX allows for more reliable GPA strain measurements. A cross-section TEM image of the resulting structure is given in Figure 4 together with the EDS line profile. They both evidence the presence of an ultra-thin Si layer (4 nm) between the Si<sub>1-x</sub>Ge<sub>x</sub> and the BOX layers, remaining from the SOI layer. From previous studies, we know that this ultra-thin layer has strong interactions with the BOX and maintains the top layer fully strained. Ge concentration is about 40 % (lower than the 50 % concentration obtained at temperatures < 800 °C) and has a diffuse interface with the Si layer as already observed in [38] [39]. There is no relaxation and no dislocations in the layers.

Figure 4: (a) TEM cross-section image of the structure after condensation at 800 °C; (b) Corresponding EDS line profile of Si, O and Ge.

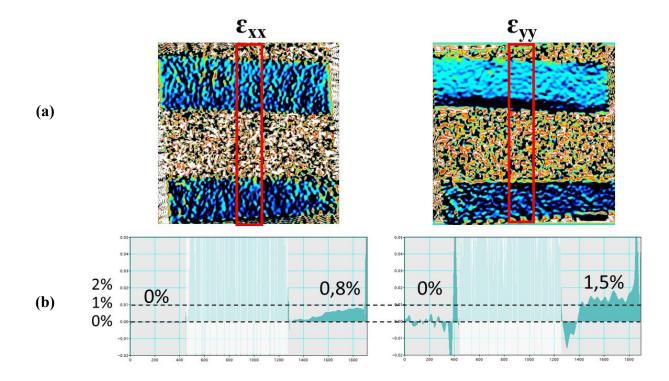

For the next step, the best mixing/homogenization results are obtained for an annealing temperature of 950 °C in RTA under N<sub>2</sub>. This method produces a strong intermixing and a homogeneous Si<sub>1-x</sub>Ge<sub>x</sub> layer (Figure 5); it also promotes atomically flat interfaces (between the cap SiO<sub>2</sub>/Si<sub>1-x</sub>Ge<sub>x</sub> and Si<sub>1-x</sub>Ge<sub>x</sub>/BOX) and low surface roughness. The Si<sub>1-x</sub>Ge<sub>x</sub> RMS roughness measured on the AFM image over  $10 \times 10 \ \mu\text{m}^2$  is below 0.1 nm (below the AFM resolution) indicating the efficiency of the method to produce high quality Si<sub>1-x</sub>Ge<sub>x</sub> relaxed template layer. The plateau in the EDS line profile confirms the uniformity of the Ge composition across the film (Figure 5b). A Ge concentration of 23 % is extracted by EDS semi-quantitative analysis.

Figure 5: (a) TEM cross-section image of the system after homogenization; (b) Corresponding EDS line profile of Si, O, and Ge.

It should be noted that the annealing temperature was chosen to lie well below the solidus line of the Si-Ge alloy phase diagram, thereby avoiding the formation of dislocations. Higher temperature annealing, resulted in nucleation of dislocations, as already observed in previous studies [42]; [43]. Fabrication of structures with partially relaxed layer free of defect were achieved for Si<sub>1-x</sub>Ge<sub>x</sub>OI with x = 0.15. For larger Ge concentrations, the layers were defective (formation of dislocations during annealing).

A critical step is the stress relaxation in the Si<sub>1-x</sub>Ge<sub>x</sub> layer upon annealing. To quantitatively map the *c*-lattice (*a*-lattice) strain on both sides of the BOX, we use the High Resolution TEM image shown in Figure 5a. GPA is then performed to the image by applying the method described in [44]. We can note artefact values of strain close to the interface with the amorphous SiO<sub>2</sub>. They are related to the integration of pixels including both crystalline and amorphous cells in the analysis. Figure 6a shows the resulting color-coded map of  $\Delta c/c$  ( $\Delta a/a$ ) in the *a*-*c* directions. The left part corresponds to the unstrained Si substrate ( $\Delta c/c = \Delta a/a = 0$  %). The right part features a deformation in the *c*-direction  $\varepsilon_{yy} = +1.5$  % and a-planes  $\varepsilon_{xx} = +0.8$  % with respect to Si (Figure 6b). These values correspond to partially relaxed Si<sub>1-x</sub>Ge<sub>x</sub> x = 0.23 as found by EDS. Unlike the sample before annealing, the distribution of the mechanical strain is constant across the layer. Importantly, while a partial relaxation is already

obtained, there is no discontinuity (or defects) in the interfacial regions for  $\Delta c/c$  and  $\Delta a/a$ , confirming the absence of misfit dislocations at the interface. This purely elastic relaxation is therefore the result of a sliding interface as already reported [36]. Overall, while GPA reveals a partial relaxation it also shows that 10 min annealing (950 °C) is not sufficient to achieve full relaxation (that would induce  $\varepsilon_{xx}$ = 1 % and  $\varepsilon_{yy}$  = 1 %) and not even the relaxation requested to significantly increase the electrons mobility.

Figure 6: (a) Color scale map of *c*-planes ( $\varepsilon_{yy}$ ) and *a*-planes ( $\varepsilon_{xx}$ ); (b) Distribution of strain integrated on areas pointed by the red squares in (a).

Several test samples were needed to validate the condensation/annealing method for forming a buffer as relaxed as possible (but without the nucleation of dislocations), the optimal annealing conditions found were: T = 970 °C, t = 30 min. The process generates an + 0.85 % relaxation of the Si<sub>1-x</sub>Ge<sub>x</sub> and ensures the absence of nucleation of dislocations during the subsequent steps.

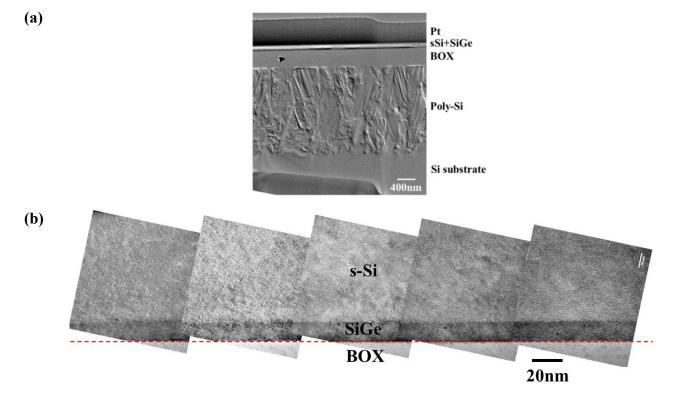

These conditions are used on the XFAB pilot samples on the bench tests. On these samples, quantitative GPA of strain is made difficult due to the excessive thickness of the oxide which makes impossible to use the Si substrate as a reference (as a matter of fact, HR images cannot include in the same image

both the top Si/Si<sub>1-x</sub>Ge<sub>x</sub> layers and the substrate). We then used Si<sub>1-x</sub>Ge<sub>x</sub> as a reference for GPA and the Ge concentration is deduced by EDS (x = 0.20 in these conditions).

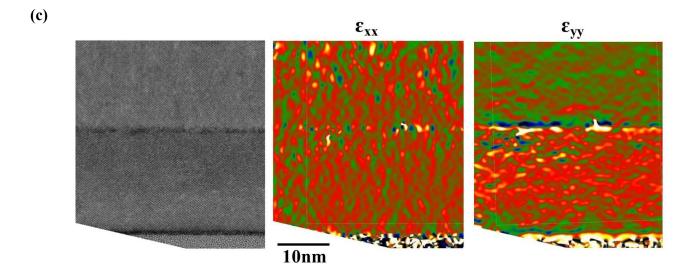

A large-scale SEM image of the device where all the constituents of the system, including poly-silicon, BOX, Si<sub>1-x</sub>Ge<sub>x</sub> + Si and Pt cap layer are visible, is given in Figure 7a. The HR-TEM image of the square area evidences the perfect crystalline quality of the sample on large scale (Figure 7b). Even more interestingly are the color-coded GPA maps of the Si/Si<sub>1-x</sub>Ge<sub>x</sub> which evidence a constant strain from Si<sub>1-x</sub>Ge<sub>x</sub> to Si in the direction parallel to the surface and an abrupt change between Si<sub>1-x</sub>Ge<sub>x</sub> (set by calibration at  $\varepsilon_{yy} = +0$  %) to the tensile strained Si (Figure 7c). From this analysis (taking Si<sub>1-x</sub>Ge<sub>x</sub> as reference) we find a tensile deformation of the Si layer  $\varepsilon_{xx} = 0$  ( $\Delta a/a$ ) and  $\varepsilon_{yy} = -0.78$  % ( $\Delta c/c$ ), not so far from the expected fully relaxed value ( $\varepsilon_{yy} = -1.1$  %).

Figure 7: (a) Large-scale TEM image of the cross-section sample on which one can see the constituents of the device, from bottom to top: Si substrate, poly-Si, BOX, Si/Si<sub>1-x</sub>Ge<sub>x</sub> and Pt cap layer; (b) HRTEM image of the Si/Si<sub>1-x</sub>Ge<sub>x</sub>/BOX system; (c) HRTEM reference image and GPA color-coded map of  $\varepsilon_{xx}$  ( $\Delta a/a$ ) and  $\varepsilon_{yy}$  ( $\Delta c/c$ ) in the *a-c*-directions.

To get a complementary insight on strain relaxation, we counted directly on the image the atomic distances and integrated the measurements on areas typically  $1000 \times 1000$  pixels. The (002) interplanar distances measured are 2.738 Å for Si<sub>1-x</sub>Ge<sub>x</sub> (x  $\approx 0.2$ ) which corresponds to a fully relaxed layer and 2.692 Å (instead of 2.715 Å for bulk Si) which corresponds to a tensile strain of - 0.85 % in good agreement with the GPA measurements.

#### 3.2 Simulations

The elastic theory is used to predict and explain the strain evolution of a Si film in epitaxy on  $Si_{1-x}Ge_x/SiO_2$  substrate (Figure 1f), as a function of experimental parameters (Si/Si<sub>1-x</sub>Ge<sub>x</sub> thicknesses and Ge concentration). We consider that during the epitaxy of Si, the Si<sub>1-x</sub>Ge<sub>x</sub> film is rigidly fixed at its lower interface to the BOX, so that this film is held in its initial strain state before Si epitaxy. In our experimental conditions, after low temperature condensation, we perform an annealing at 970 °C which homogenizes the Ge concentration throughout the (Si + Si<sub>1-x</sub>Ge<sub>x</sub>) layer. At this temperature, the viscous flow of the BOX provides an efficient elastic relaxation without dislocation nucleation. Consequently, in the simulations, we impose

a displacement vector at the Si<sub>1-x</sub>Ge<sub>x</sub>/BOX interface which is zero with respect to the relaxed state. This condition introduces finite size effects compared to the semi-infinite layer where one imposes the displacement vector to be zero in the  $z \rightarrow -\infty$  limit.

We note  $h_{tot} = h + e$  the total thickness, with h(e) the Si (Si<sub>1-x</sub>Ge<sub>x</sub>) thickness (Figure 1f). The Si free surface is located at  $z = H(\mathbf{r})$ , where  $\mathbf{r} = (x, y)$ . We use the theory of linear and isotropic elasticity where the strain  $\varepsilon$  and stress  $\sigma$  tensors are linearly related [45] thanks to the Young's modulus Y and Poisson's ratio v that are supposed to be identical in the Si and Si<sub>1-x</sub>Ge<sub>x</sub>. Stress arises from the lattice mismatch between the film (Si) and the substrate (Si<sub>1-x</sub>Ge<sub>x</sub>), characterized by the misfit  $m = 1 - a^{f}/a^{s}$ , with  $a^{f(s)}$  is the film (substrate) lattice parameter. In the following, we compute all strain vectors u with respect to a reference state defined with the substrate lattice parameter  $a^{s}$ . Mechanical equilibrium enforces the relation  $\nabla \cdot \sigma = 0$  and the strain state is determined with the boundary conditions. The substrate lower surface is supposed to be rigid and is set at its relaxed lattice parameter, so that:

$$u(z=0)=0\tag{1}$$

This situation dramatically changes the strain state compared to the deposition on a crystalline softer or stronger substrate [46]; [47]. As usual, the top surface is supposed to be free of stress,  $\sigma$   $n(z = h_{tot}(r)) = 0$ , while the film/layer interface is coherent so that  $u(z=e^{-}) = u(z=e^{+})$  and

$$\sigma n_z (z = e^-) = \sigma \cdot n_z (z = e^+)$$

In the case of a flat film, i.e. when  $H(r) = h_{tot}$  is constant, we find the solution:

$$u_0 = \left(0, 0, m \frac{1+\nu}{1-\nu}(z-e)\right)$$

in the Si film, while  $u_0$  vanishes in Si<sub>1-x</sub>Ge<sub>x</sub>. This solution is associated with an elastic energy density  $\varepsilon_0 = \frac{Ym^2}{1-\nu}$ . Contrarily to the case where the lower layer surface is free of stress [48], in our current conditions, the flat film solution does not depend on the ratio  $e/h_{tot}$ , and there is no strain sharing between the film and the substrate.

When the film is modulated with a small corrugation,  $H(\mathbf{r})=h_{tot}+h_1(\mathbf{r})$ , the displacement vector may be expanded at first order in the surface slope [49] as  $u=u_0+u_1$  where  $u_1$  is conveniently found in Fourier space in the *x* and *y* directions, with a wave vector *k*. The solution of the mechanical equilibrium involves here both  $e^{kz}$  and  $e^{-kz}$  terms, both in Si and Si<sub>1-x</sub>Ge<sub>x</sub> layers. Eventually, one finds  $u_1(k)$  and the elastic energy density on the surface  $\varepsilon = \varepsilon_0 + \varepsilon_1$  where  $\varepsilon_1$  is given by

$$\varepsilon_1(k) = -2(1+\nu) \ \varepsilon_0 A_k(kh_{tot})kh_1(k), \tag{2}$$

in Fourier space, with

$$A_k(x) = \frac{(3-4\nu)sh(2x)+2x}{(3-4\nu)ch(2x)+2x^2+\frac{1}{2}[1+(3-4\nu)^2]}$$

(3)

Note again that the finite size effects at first order depend here solely on  $h_{tot}$ . This result coincides with the large thickness limit  $h_{tot} \rightarrow \infty$  in the semi-infinite substrate case (large Si<sub>1-x</sub>Ge<sub>x</sub> thickness) [50] where  $A_k = 1$ . More interestingly, it also corresponds to the  $s \rightarrow \infty$ limit of [47] describing a film/substrate system deposited on a crystalline soft substrate with a Young modulus  $Y^{sub} = sY$ . In our current situation (rigid interface) one finds that at low-k,

$$A_k(kh_{tot}) = \frac{kh_{tot}}{1-\nu} + O(kh_{tot})$$

(4)

Consequently,  $\varepsilon_1(k)$  is analytic and no longer singular as |k| in the  $k \to 0$  limit, contrarily to the usual elastic relaxation in the semi-infinite or soft cases. In particular, in the film/soft substrate (*fss*) case [46], [47], one finds  $A_k^{fss} = 1/s + O(kh_{tot})$  that only renormalizes the elastic energy density  $\varepsilon_1(k)$  by 1/s at low k-e elastic stress described by (2) may be relieved by the morphological evolution of the surface, as generically described by the Asaro-Tiller-Grinfeld instability [51], [52]. Mass conservation enforces the diffusion equation [53]  $\partial h/\partial t = D\Delta_s \mu$  where D is a diffusion constant, and  $\Delta_s$ , the surface Laplacian. The chemical potential  $\mu$  is the sum of the elastic energy density and surface energy  $\gamma(h)\kappa$ , where  $\gamma(h)$  is the surface energy and  $\kappa = -(h_{xx} + h_{yy})$  the surface mean curvature. The h-dependence of the surface energy describes the wetting effects [49]. In epitaxial systems, it may be given by  $\gamma(h)$ = [ $\gamma_f 1 + c_w e^{-h/\partial_w}$ ] after inspection of atomistic results [54]. Given the solution for the elastic energy, one finds that a modulation of wave-vector k grows in the linear approximation as  $h_1(k, t)=e^{ik\cdot r+\sigma t}$  with

$$\sigma(k, h_{tot}, h) = -\frac{c_{\omega}}{\delta_{\omega}^2} e^{-\frac{h}{\delta_{\omega}}} k^2 + A_k(kh_{tot})k^3 - k^4$$

(5)

in units of the space and time scales  $l_0 = \gamma_f / [2(1+v)\varepsilon_0]$  and  $t_0 = l^4 / D\gamma_f$ . Due to the presence of both the wetting and the finite-size elastic effects, the growth rate depends both on  $h_{tot}$  and h.

The first striking outcome of this analysis is that even without wetting interactions ( $c_w = 0$ ), the rigid substrate introduces a new critical thickness  $h_c^0$  below which ( $h < h_c^0$ ),  $\sigma(k)$  is negative and the instability is inhibited. Indeed, when  $c_w = 0$ , the small-*k* expansion of  $\sigma$  is

$$\sigma = -\left(1 - \frac{h_{tot}}{h_c^0}\right)k^4 + O(k^6)$$

(6)

with

$$h_c^0 = 1 - \nu \tag{7}$$

in dimensionless units. A similar result was found in [53] in the case of a rigid substrate. It is noticeable that  $h_c^0$  only depends on a combination of elastic and surface effects and results from the lowering of the elastic relaxation due to the rigid interface [55]. In our experimental conditions, the interface rigidity weakens the instability development below a given thickness. This inhibition is thence inferred to elastic relaxation inhibition (i.e. it is not the consequence of wetting interactions). Conversely, an increased softness promotes the instability as the elastic cost in a softer substrate (associated with the elastic relaxation) is lowered [46], [47].

Another limit concerns the semi-infinite case where Si<sub>1-x</sub>Ge<sub>x</sub> is a very thick substrate  $(h_{tot} \rightarrow +\infty)$  while the Si film has a finite thickness (h). In these conditions, if we consider wetting interactions  $(c_{\omega} \neq 0)$ , there is another critical thickness below which the morphological evolution cannot occur (when wetting interactions are sufficiently damped to allow strain relaxation). It corresponds to the ATG instability  $(h_c^{ATG})$  in presence of wetting where  $h_c^{ATG} = \delta_{\omega} log\left(\frac{4c_{\omega}}{\delta_{\omega}^2}\right)$  [49]. In these conditions,  $A_k = 1$  and we find that below  $h_c^{ATG}$ ,  $\sigma(k)$  is always negative, while above  $h_c^{ATG}$ ,  $\sigma(k)$  displays a range of wave-vectors where it is positive, so that a morphological instability can grow.

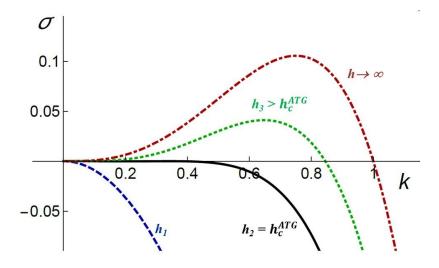

Figure 8: Growth rate of the elastic instability as a function of its wavevector k for a given layer thickness e and for  $h_1 < h_c^{ATG}$  (dashed blue line),  $h_2 = h_c^{ATG}$  (solid black line),  $h_3 > h_c^{ATG}$

(dotted green line) and in the  $h \rightarrow +\infty$  limit (dash-dotted red line). The length and time scales are  $l_0$  and  $t_0$ . We choose  $c_{\omega} = 0.1$ ,  $\delta_{\omega} = 0.01$ , v = 0.273, a given e = 1 - v, while  $h_1 = 0.07$ ,  $h_2 = 0.116$  and  $h_3 = 1$ .

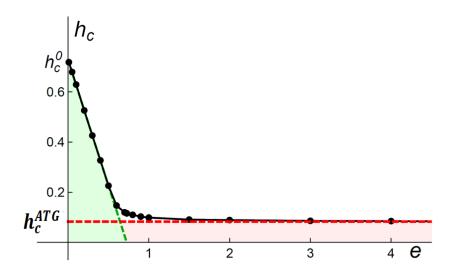

In the general case, with both wetting interactions and a finite thickness  $h_{tot}$ , one finds a Stranski-Krastanov like behavior (Figure 8). Below the  $h_c^{ATG}$  critical thickness, that a priori depends on the layer thickness e, the growth rate is negative and the instability is inhibited ( $h_1$ ). The Si film remains fully strained and flat. Conversely, for  $h > h_c^{ATG}$ , the instability grows and strain relaxation spreads through the Si film  $(h_3)$ .  $h_c^{ATG}$  has two major specificities, first it depends only on *e* as a result of the combination of both the elastic inhibition and wetting interactions and second, its value is of the order of the instability length scale  $l_0$  which is of the order of hundreds of nanometers in our experimental conditions, well above the Si thickness (70 nm) deposited for the targeted device. The typical dependence of  $h_c(e)$  is plotted in Figure 9. When  $e \to +\infty$ ,  $h_{tot}$  also diverges and the instability growth rate coincides with the semi-infinite substrate case  $(h_c(e) \rightarrow h_c^{ATG})$ . On the contrary, when  $e \rightarrow 0$ ,  $h_c(e)$  nearly coincides with  $h_c(e) \approx h^0 - e$ . In between these two limits,  $(0 \le A_k \le 1 \text{ for } v \le \frac{1}{2})$  $\sigma(k, h_{tot}, h)$  (and strain relaxation) is always much reduced compared with the normal ATG situation. In presence of wetting interactions,  $\sigma(k, h_{tot}, h)$  is even lower than without wetting interactions, and the instability only develops when  $h_{tot} \ge h^0$  with  $h_c(e) \ge h^0 - e$  which in our experimental conditions correspond to 83 nm (for x = 0.2 and e = 19 nm)

As a conclusion, the calculations show that strain relaxation will occur when  $h_c(e) \ge \sup(h_c^{ATG}, h^0 - e)$ . This condition is indeed satisfied in the numerical solution for  $h_c(e)$  plotted in Figure 9.

Figure 9: Numerical solution for  $h_c(e)$  above which the instability grows, as a function of the layer thickness e, with the parameters described in Figure 8 and in units of  $l_0$ .

#### 3.3 Discussion

During this study we blew out crucial locks that were blocking the fabrication of Si. First the strain relaxation of Si<sub>1-x</sub>Ge<sub>x</sub> (SGOI) which must be achieved without change of the uniformity and flatness and without dislocation nucleation. In these layers, strain relaxation commonly occurs by the introduction of 60° perfect dislocations or planar defects, such as microtwins and stacking faults that are associated with loss of coherency during oxidation/annealing. In addition to this extended defect mechanism, the buckling of thin SGOI films has been demonstrated as another mechanism which explains the discrepancy between thermodynamically predicted strain levels and experimental results [56]. When the system is deposited on a SiO<sub>2</sub> viscous layer, the buckling rate of the SGOI film (i.e. the inverse of the bucking time constant  $\tau_B$ ) can be expressed using the Föppl von Kármán plate equation which describes the large deflection of thin compressed films with:

$$\frac{1}{\tau_B} = \frac{E}{12\eta(1-\eta^2)} \left[ \frac{\sinh(2h_{SiO_2}k) - 2h_{SiO_2}k}{1 + \cosh(2h_{SiO_2}k) + 2(h_{SiO_2}k)^2} \right] \times [12e(1-\nu)ek - (ek)^2]$$

where  $\eta$  is the viscosity of SiO<sub>2</sub>,  $h_{SiO2}$  the thickness of SiO<sub>2</sub> and k the wavenumber of a particular buckling mode [56]. In these conditions, the relaxation of SGOI strain, below the glass transition temperature ( $\approx 1100$  °C) has the same activation energy as viscous flow and is controlled by the viscosity [57] which varies with temperature following an Arrhenius relation. In our experimental conditions, after low temperature condensation (800 °C), Si<sub>1-x</sub>Ge<sub>x</sub> layer (x=0.4 and  $h_{Si1-xGex} \approx$ 12 nm) is fully strained on SOI (as already reported [38] [39]). The critical step is then to transform this fully strained Ge rich layer into relaxed SGOI (preferably fully relaxed). In addition, as deduced from the simulations, Si<sub>1-x</sub>Ge<sub>x</sub> should have low thickness and concentration to avoid elastic strain relaxation (since  $h_c(e)$  and x are directly related). For the targeted device, the layer should also be homogeneous in concentration, flat (no buckling), and free of dislocation. The results show that at a very crucial temperature annealing (T  $\approx$  950 °C) both homogenizing of the concentration throughout  $(Si + Si_{1-x}Ge_x)$  and strain relaxation are optimal. It provides the fabrication of a perfectly flat Si<sub>1-x</sub>Ge<sub>x</sub> template layer with x = 0.23 % and  $e \approx 20$  nm. In addition, at this temperature (i.e. below the glass transition temperature), SiO<sub>2</sub> has a low viscosity which could allow a slow layer by layer redistribution of  $Si_{1-x}Ge_x$  slightly pushing  $SiO_2$  in a planar way which would provide elastic strain relaxation without buckling [58]. The annealing is also very efficient to flatten the Si<sub>1-x</sub>Ge<sub>x</sub>/BOX interface. The temperature of annealing is here very crucial since at lower temperature, strain is not relaxed (SiO<sub>2</sub> is too rigid) while at higher temperature, there is nucleation of dislocations.

The second tricky step is the epitaxy of Silicon which should lead to expitaxial Si, fully strained on Si<sub>1-x</sub>Ge<sub>x</sub>. As demonstrated by elastic theory, epitaxy should be performed at low enough temperature (500 °C) to have a rigid Si<sub>1-x</sub>Ge<sub>x</sub>/BOX interface and avoid strain sharing, as reported in the simulations. Indeed, strain sharing is forbidden only when the interface is rigid. It is roughly explained by the energy cost (when the interface becomes very rigid) to relax strain at this interface which becomes too large as compared to the gain of relaxation energy. In addition, the simulations also show that *e* should be lower than the critical thickness  $h_c(e)$  where corrugation development starts as a consequence of Si strain relaxation (Figure 8). We have shown that it is the combination of all these very specific parameters chosen on the basis of elastic simulations that allow to get the fully strained Si layer as demonstrated here.

#### 4. Conclusion

Thanks to a multi-disciplinary approach based on elastic modelling and series of highly specialized experiments, we have developed a simple process for engineering tensile strained Si layers on a relaxed SGOI film using parameters precisely fitted to theoretical predictions. Contrary to the previous processes reported in the literature, the present method allows to fabricate defectless layers thanks to a fine tuning of experimental parameters: Si<sub>1-x</sub>Ge<sub>x</sub> composition and thickness and temperatures of epitaxy, condensation and annealing. The three crucial steps are: (i) fabrication of ultra-thin Ge rich Si<sub>1-x</sub>Ge<sub>x</sub> layer by low temperature condensation, (ii) relaxation and homogenization of SOI/Ge rich Si<sub>1-x</sub>Ge<sub>x</sub> layer during annealing without dislocation nucleation nor buckling. Elastic relaxation results from the low BOX viscosity at high temperature, which would promote a slow layer by layer  $Si_{1-x}Ge_x$  matter redistribution (iii) Si epitaxy without strain sharing, producing defect-free, planar and fully strained Si. Elastic simulations show that inhibition of strain sharing is only made possible if  $Si_{1-x}Ge_x$  buffer layer is thin and rigidly fixed to the BOX. The process reliably and reproducibly produces a Si layer under - 0.85 % tensile strain. According to the literature, such tensile strain should lead to 110 % increase of the electron mobility, and thus significantly decrease the Ron\*Coff figure of merit of RF-switches. The developed process is applied to the pilot large multifinger 2.5 V n-type MOSFET on SOI used for RF-switches applications of XFAB. The electrical characteristics foreseen place it at the top level of the components made in the world. The developed process is simple and generic and can be adapted to many other devices.

#### Funders

L.F., M.A., A.R. and I.B. would like to thank Nanotecmat and CP2M platforms for providing elaboration and characterization equipments. T.D., N.P., F.D., P.C., and G.U. are grateful to NANO2022 for financial support.

#### **Author Contributions**

I.B. and G.U. conceived the project; I.B., N.P., F.D. and G.U. conceived and designed the experiments and supervised the work, T.D. performed the MBE experiments, T.D. and L.F. performed TEM experiments and GPA analyses. L.F., M.A., A.R. and I.B. interpreted the results,

J.N.A. developed the theoretical model and made the calculations. All authors contributed to the scientific discussions, manuscript preparation, and final revision. The manuscript was written through contributions of all authors. All authors have given approval to the final version of the manuscript.

\*Corresponding authors: <u>isabelle.berbezier@im2np.fr;</u> <u>luc.favre@im2np.fr;</u>

#### References

- Samavedam, S. B.; Fitzgerald, E. A. "Novel Dislocation Structure and Surface Morphology Effects in Relaxed Ge/Si-Ge(graded)/Si Structures," J. Appl. Phys., 1997, 81, 3108-3116.

- [2] O'Neill, A. G.; Routley, P.; Gurry, P. K.; Clifton, P. A.; Kemhadjian, H.; Fernandez, J.; Cullis, A. G.; and Benedetti, A. "SiGe Virtual Substrate N-Channel Heterojunction MOSFETs," Semicond. Sci. Technol., 1999, 14, 784-789.

- [3] Mizuno, T.; Takagi, S.; Sugiyama, N.; Satake, H.; Kurobe, A.; and Toriumi, A. "Electron and Hole Mobility Enhancement in Strained-Si MOSFET's on SiGe-On-Insulator Substrates Fabricated by SIMOX Technology," IEEE Electron Device Letters, 2000, 21, 230-232.

- [4] Rim, K.; Hoyt, J. L.; and Gibbons, J. F. "Fabrication and Analysis of Deep Submicron Strained-Si N-MOSFET's," *IEEE Trans Electron Dev*, 2000, 47, 1406-1415.

- [5] Thompson, S.; Anand, N.; Armstrong, M.; Auth, C.; Arcot, B.; Alavi, M.; Bai, P.; Bielefeld, J.; Bigwood, R.; Brandenburg, J.; Buehler, M.; et al. "A 90 nm Logic Technology Featuring 50 nm Strained Silicon Channel Transistors, 7 Layers of Cu Interconnects, Low k ILD, and 1 /spl mu/m/sup 2/ SRAM Cell," *Dig. IEDM 2002*, 2002, 61-64.

- [6] Goo, J.; Xiang, Q.; Takamura, Y.; Wang, H.; Pan, J.; Arasnia, F.; Paton, E.; Besser, P.; Sidorov, M.; Adem, E.; Lochtefeld, A.; Braithwaite, G.; Currie, M.; Hammond, R.; Bulsara, M.; and Lin, M. "Scalability of Strained-Si nMOSFETs Down to 25 nm Gate Length," *IEEE ELECTRON DEVICE LETTERS*, 2003, 24, 351-353.

- [7] Olsen, S. H.; O'Neill, A. G.; Chattopadhyay, S.; Kwa, K. S. K.; Driscoll, L. S.; Norris, D. J.; Cullis, A. G.; Robbins, D. J.; and Zhang, J. "Evaluation of Strained Si/SiGe Material for High Performance CMOS," *Semicond. Sci. Technol.*, 2004, 19, 707-714.

- [8] Sugii, N.; Hisamoto, D.; Washio, K.; Yokoyama, N.; Kimura, S.; «Performance Enhancement of Strained-Si MOSFETs Fabricated on a Chemical-Mechanical-Polished SiGe Substrate,» *IEEE Trans. Electron Dev.*, 2002, 49, 2237-2243.

- [9] Rim, K.; Hoyt, J. L.; and Gibbons, J. "Transconductance Enhancement in Deep Submicron Strained Si n-MOSFETs," *Tech. Dig. IEDM*, 1998, 707-710.

- [10] Ungersboeck, E.; Dhar, S.; Karlowatz, G.; Sverdlov, V.; Kosina, H.; and Selberherr, S. "The Effect of General Strain on the Band Structure and Electron Mobility of Silicon," *IEEE Trans. Electron Devices*, 2007, 54, 2183-2190.

- [11] Reiche, M.; Moutanabbir, O.; Hoentschel, J.; Gösele, U.; Flachowsky, S.; and Horstmann,M. "Strained Silicon Devices," *Solid State Phenomena*, 2010, 156-158, 61-68.

- [12] Flachowsky, S.; Wei, A.; Illgen, R.; Herrmann, T.; Hontschel, J.; Horstmann, M.; Klix, W.; and Stenzel, R. "Understanding Strain-Induced Drive-Current Enhancement in Strained-Silicon n-MOSFET and p-MOSFET," *IEEE Trans. Electron Devices*, 2010, 57, 1343-1354.

- [13] Fernandez, J. M.; Matsumara, A.; Zhang, X. M.; Xie, M. H.; Hart, L.; Zhang, J.; Joyce, B.A.; and Thornton, T. J. "Two Dimensional Electron Gases in SiGe/Si Heterostructures Grown

by Gas Source Molecular Beam Epitaxy," J. of Mat. Scie.: Mat. in Electronics, 1995, 6, 330-335.

- [14] Abstreiter, G.; Brugger, H.; Wolf, I.; Jorke, H.; and Herzog, H. J. "Strain-Induced Two-Dimensional Electron Gas in Selectively Doped Si/SixGe1-x Superlattices," *Phys. Rev. Lett.*, 1985, 54, 2441-2444.

- [15] Berbezier, I.; Gallas, B.; and Derrien, J. "Elastic Strain Relaxation in Si1-xGex Layers Epitaxially Grown on Si Substrates," *Surf. Review and Lett.*, 1998, 5, 133-138.

- [16] Gallas, B.; Hartmann, J. M.; Berbezier, I.; Abdallah, M.; Zhang, J.; Harris, J. J.; and Joyce,

B. A. "Influence of Misfit and Threading Dislocations on the Surface Morphology of SiGe

Graded-Layers," J. of Cryst. Growth, 1999, 201, 547-550.

- [17] Perova, T. S.; Wasyluk, J.; Lyutovich, K.; Kasper, E.; Oehme, M.; Rode, K.; and Waldron,

A. "Composition and Strain in Thin Si1–xGex Virtual Substrates Measured by Micro-Raman

Spectroscopy and X-ray Diffraction," *Journal of Applied Physics*, 2011, 109, 1-11.

- [18] Bauer, M.; Lyutovich, K.; Oehme, M.; Kasper, E.; Herzog, H. J.; and Ernst, F. "Relaxed SiGe Buffers with Thicknesses Below 0.1 μm," *Thin Solid Films*, 2000, 369, 152-156.

- [19] Fitzgerald, E. A.; Kim, A. Y.; Currie, M. T.; Langdo, T. A.; Taraschi, G.; and Bulsar, M. T.

"Dislocation Dynamics in Relaxed Graded Composition Semiconductors," *Materials Science and Engineering: B*, 1999, 67, 53-61.

- [20] Currie, M. T.; Samavedam, S. B.; Langdo, T. A.; Leitz, C. W.; and Fitzgerald, E. "Controlling Threading Dislocation Densities in Ge on Si using Graded SiGe Layers and Chemical-Mechanical Polishing," *Appl. Phys. Lett.*, 1998, 72, 1718-1720.

- [21] Lee, M. L.; Fitzgerald, E. A.; Bulsara, M. T.; Currie, M. T.; and Lochtefeld, A. "Strained Si, SiGe, and Ge Channels for High-Mobility Metal-Oxide-Semiconductor Field-Effect Transistors," *J.of Appl. Phys.*, 2005, 97, 011101, 2005.

- [22] Olsen, S. H.; O'Neill, A. G.; Driscoll, L. S.; Kwa, K. S. K.; Chattopadhyay, S.; Waite, A. M.; Tang, Y. T.; Evans, A. G. R.; Norris, D. J.; Cullis, A. G.; Paul, D. J.; and Robbins, D. J. "High-Performance nMOSFETs Using a NovelStrained Si/SiGe CMOS Architecture," *IEEE Trans. on Electron Devices*, 2003, 50, 1961-1969.

- [23] Sugii, N.; Nakagawa, K.; Yamaguchi, S.; and Miyao, M. "Role of Si1-xGex Buffer Layer on Mobility Enhancement in a Strained-Si n-Channel Metal–Oxide–Semiconductor Field-Effect Transistor," *Appl. Phys. Lett.*, 1999, 75, 2948-2950.

- [24] Kumar, M. J.; Singh, T. V. «Quantum Confinement Effects in Strained Silicon MOSFETs,» Int. J. Nanosci., 2008, 7, 81-84.

- [25] Kitagawa, I.; Maruizumi, T.; and Sugii, T. "Theory of Electron-Mobility Degradation Caused by Roughness with Long Correlation Length in Strained-Silicon Devices," J. Appl. Phys., 2003, 94, 465-470.

- [26] Aubry-Fortuna, V.; Dollfus, P.; and Galdin-Retailleau, S. "Electron Effective Mobility in Strained Si/Si1-xGex MOS Devices using Monte Carlo Simulation," *Solid State Electronics*, 2005, 49, 1320-1329.

- [27] Suh, J.; Nakane, R.; Taoka, N.; Takenaka, M.; and Takagi, S. "Effects of Additional Oxidation After Ge Condensation on Electrical Properties of Germanium-On-Insulator p-Channel MOSFETs," *Soid State Electron.*, 2016, 117, 77-87.

- [28] Kim, K.; Chuang, C. T.; Rim, K. and Joshi, R. V. "Performance Assessment of Scaled Strained-Si Channel-On-Insulator (SSOI) CMOS," *Solid-State Electron.*, 2004, 48, 239-243.

- [29] Langdo, T.; Currie, M. T.; Cheng, Z. Y.; Fiorenza, J. G.; Erdtmann, M.; Braithwaite, G.; Leitz, C.; Vineis, C.; Carlin, J.; Lochtefeld, A.; Bulsara, M. T.; Lauer, I.; Antoniadis, D. A. and Somerville, M. "Strained Si On Insulator Technology: From Materials to Devices," *Solid State Electronics*, 2004, 48, 1357-1367.

- [30] Boucaud, P.; El Kurdi, ;M. and Hartmann, J. M. "Photoluminescence of a Tensilely Strained Silicon Quantum Well on a Relaxed SiGe Buffer Layer," *Appl. Phys. Lett.*, 2004, 85, 46-48.

- [31] Tezuka, T.; Nakaharai, S.; Moriyama, Y.; Sugiyama, N.; and Takagi, S. "High-mobility strained SiGe-on-insulator pMOSFETs with Ge-rich surface channels fabricated by local condensation technique," *IEEE Electron Device Lett.*, 2005, 26, 243-245.

- [32] Souriau, L.; Terzieva, V.; Vandervorst, W.; Clemente, F.; Brijs, B.; Moussa, A.; Meuris, M.;

Loo, R.; and Caymax, M. «High Ge Content SGOI Substrates Obtained by the Ge

Condensation Technique: A Template for Growth of Strained Epitaxial Ge,» *Thin Solid Films*, 2008, 517, 23-26.

- [33] Jain, J. R.; Ly-Gagnon, D. S.; Balram, K. C.; White, J. S.; Brongersma, M. L.; Miller, D. A.

B.; and Howe, R. T. "Tensile-Strained Germanium-On-Insulator Substrate Fabrication for Silicon-Compatible Optoelectronics," *Opt. Mater. Express*, 2011, 1, 1121-1126,.

- [34] Lin, G.; Liang, D.; Wang, J.; Yu, C.; Li, C.; Chen, S.; Huang, W.; Wang, J.; and Xu, J. "Strain Evolution in SiGe-On-Insulator Fabricated by a Modified Germanium Condensation Technique with Gradually Reduced Condensation Temperature," *Materials Science in Semiconductor Processing*, 2019, 97, 56-61.

- [35] Hutin, L.; Royer, C. L.; Damlencourt, J.; Hartmann, J. M.; Grampeix, H.; Mazzocchi, V.; Tabone, C.; Previtali, B.; Pouydebasque, A.; Vinet, M.; and Faynot, O. "GeOI pMOSFETs Scaled Down to 30-nm Gate Length With Record Off-State Current," *IEEE Electron. Device Lett.*, 2010, 31, 234-236.

- [36] Boureau, V.; Reboh, S.; Benoit, D.; Hÿtch, M.; and Claverie, A. "Strain Evolution of SiGe-On-Insulator Obtained by the Ge-Condensation Technique," *Appl. Phys. Lett. Mat.*, 2019, 7, 041120.

- [37] Gunji, M.; Marshall, A. F.; and McIntyre, P. C. "Strain Relaxation Mechanisms in Compressively Strained Thin SiGe-On-Insulator Films Grown by Selective Si Oxidation," J. of Appl. Phys., 2011, 109, 014324.

- [38] David, T.; Benkouider, A.; Aqua, J. N.; Cabie, M.; Favre, L.; Neisius, T.; Abbarchi, M.; Naffouti, M.; Ronda, A.; Liu, K.; and Berbezier, I. "Kineticsand Energetics of Ge Condensation in SiGe Oxidation," *J. Phys. Chem. C*, 2015, 119, 24606-24613.

- [39] David, T.; Liu, K.; Fernandez, S.; Richard, M. I.; Ronda, A.; Favre, L.; Abbarchi, M.; Benkouider, A.; Aqua, J. N.; Peters, M. C.; Voorhees, P. W.; Thomas, O. and Berbezier, I. "Remarkable Strength Characteristics of Defect-Free SiGe/Si Heterostructures Obtained by Ge Condensation," *J. Phys. Chem. C*, 2016, 120, 20333-20340.

- [40] Aqua, J. N.; Berbezier, I.; Favre, L.; Frisch, T.; and Ronda, A. "Growth and Self-Organization of SiGe Nanostructures," *Phys. Rep.*, 2013, 522, 59-189.

- [41] Berbezier, I.; and Ronda, A. "SiGe Nanostructures," Surf. Scie. Rep., 2009, 64, 47-98.

- [42] An, Z.; Wu, Y.; Zhang, M.; Di, Z.; Lin, C.; Fu, R. K. Y.; Chen, P.; Chu, P. K.; Cheung, W.Y. and Wong, S. P.; "Relaxed Gilicon-germanium-On-Insulator Substrates by Oxygen

Implantation Into Pseudomorphic Silicon Germanium Silicon Heterostructure," *Appl. Phys. Lett.*, 2003, 82, 2452-2454.

- [43] Nakaharai, S.; Tezuka, T.; Sugiyama, N.; Moriyama, Y.; and Takagi, S. "Characterization of 7-nm-Thick Strained Ge-On-Insulator Layer Fabricated by Ge-Condensation Technique," *Appl. Phys. Lett.*, 2003, 83, 3516-3518.

- [44] Hytch, M. J.; Snoeck, E.; and Kilaas, R. "Quantitative Measurement of Displacement and Strain Fields From HREM Micrographs," *Ultramicroscopy*, 1998, 74, 131-146.

- [45] Landau, L.; and Lifchitz, E. "Theory of Elasticity," in Course of theoretical physics, 1986.

- [46] Berbezier, I.; Aqua, J. N.; Aouassa, M.; Favre, L.; Escoubas, S.; Gouyé, A.; and Ronda, A.

"Accommodation of SiGe Strain on a Universally Compliant Porous Silicon Substrate," *Phys. Rev. B*, 2014, 90, 035315-035320.

- [47] Aqua, J. N.; Favre, L.; Ronda, A.; Benkouider, A.; and Berbezier, I. "Configurable Compliant Substrates for SiGe Nanomembrane Fabrication," *Crystal Growth & Design*, 2015, 15, 3399-3406.

- [48] Mezaguer, M.; Ouahioune, N.; and Aqua, J. N. "When Finite-Size Effects Dictate the Growth Dynamics on Strained Freestanding Nanomembranes," *Nanoscale Adv.*, 2020, 2, 1161-1167.

- [49] Aqua, J. N.; Frisch, T.; Verga, A.; «Nonlinear Evolution of a Morphological Instability in a Strained Epitaxial Film,» *Phys. Rev. B*, 2007, 76, 165319.

- [50] Aqua, J. N.; and Frisch, T. "Influence of surface energy anisotropy on the dynamics of quantum dot growth," *Phys. Rev. B*, 2010, 82, 085322.

- [51] Asaro, R. J.; and Tiller, W. A. "Interface morphology development during stress corrosion cracking: Part I. Via surface diffusion," *Metallurgical and Materials Transactions B*, 1972, 3, 1789–1796.

- [52] Grinfeld, M. A. "Instability of the Interface Between a Nonhydrostatically Stressed Elastic Body and a Melt," *Akademiia Nauk SSSR, Doklady*, 1986, 290, 1358-1363.

- [53] Spencer, B. J.; Voorhees, P. W.; and Davis, S. H. "Morphological Instability in Epitaxially Strained Dislocation-Free Solid Films," *Phys. Rev. Lett.*, 1991, 67, 3696-3699.

- [54] Lu, G. H.; and Liu, F. "Towards Quantitative Understanding of Formation and Stability of Ge Hut Islands on Si(001)," *Phys. Rev. Lett.*, 2005, 94, 176103

- [55] Note: see the vanishing of Ak at low-k given in (4), as opposed to the semi-infinite substrate case where Ak = 1.

- [56] Gunji, M.; Marshall, A. F.; and McIntyre, P. C. "Strain Relaxation Mechanisms in Compressively Strained Thin SiGe-On-Insulator Films Grown by Selective Si Oxidation," *Journal of Applied Physics*, 2011, 109, 014324-1-014324-6.

- [57] Doremus, R. H. "Viscosity of Silica," Journal of Applied Physics, 2002, 92, 7619-7629.

- [58] Assaf, E.; Berbezier, I.; Bouabdellaoui, M.; Abbarchi, M.; Ronda, A.; Valenducq, D.;Gourhant, O.; Deprat, F.; Dutartre, D.; Favre, L., submitted