# DEv-PROMELA: modeling, verification, and validation of a video game by combining model-checking and simulation

Aznam Yacoub, Maamar El Amine Hamri, Claudia Frydman

### ▶ To cite this version:

Aznam Yacoub, Maamar El Amine Hamri, Claudia Frydman. DEv-PROMELA: modeling, verification, and validation of a video game by combining model-checking and simulation. SIMULATION: Transactions of The Society for Modeling and Simulation International, 2020, 96 (11), 10.1177/0037549720946107. hal-03538522

## HAL Id: hal-03538522 https://amu.hal.science/hal-03538522v1

Submitted on 25 Apr 2023

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# DEv-PROMELA: Modelling, Verification and Validation of a Video Game by Combining Model-Checking and Simulation

SIMULATION: Transactions of The Society for Modeling and Simulation International

XX(X):1–27

©The Author(s) 2020

Reprints and permission:

sagepub.co.uk/journalsPermissions.nav

DOI: 10.1177/ToBeAssigned

www.sagepub.com/

SAGE

Aznam Yacoub<sup>1</sup>, Maâmar El-Amine Hamri<sup>1</sup> and Claudia Frydman<sup>1</sup>

### **Abstract**

Modelling, Verifying and Validating are essential steps in order to build systems and software that do what designers expect. If Formal Verification, and especially Model-Checking, is a popular method for proving correctness of proporties, its efficiency depends on the accuracy of the used models, and the quality of abstractions. As a consequence, applying verification techniques on large-scale complex software like video games is hard without strong assump and simplifications. Simulation models are generally more accurate than verification models, but it is often like harder to verify them. Combined formalisms that take benefits of both Model-Checking and Discrete-Event Simulation, represent a good deal between these both families, althought strong engineering expertise remains necessary to define the relevant tests and scenarios. This paper proposes an approach to build this kind of formalisms through the example of DEv-PROMELA, which is built by combining DEVS formalism and PROMELA language. Then, it shows how combined formalisms can be used for Modelling, Veryfing and Validating complex software like video games by using both formal-based and simulation-based Verification and Validation.

### Keywords

Model Checking, Verification and Validation, Modelling and Simulation, DEVS, PROMELA, DEV-PROMELA

### 1 Introduction

### 1.1 Motivation

The need for elaborate techniques for designing and developing systems has been well recognized in recent years. Building reliable systems, hardware or sol ware has become harder, due to the complex behaviours and interactions between their components. This complexity makes harder the understanding of the real behaviours compared to the expected behaviours, and makes harder preventing bugs and defects. Moreover, it is also harder to perform tests directly on the target system, although Verification and Validation (V&V) techniques have deceply changed the last decades hen, it is well-known that designers must think on representations of systems and software. However, the size models grows up with the complexity of systems. For this reason, plenty of new V&V concepts, methods and tools have been proposed over the past 20 years to make safer or more efficient V&V of models [2, 3]. These techniques can be classified in two great families.

Formal Verification. On the one hand, Formal Verification (FV), with Formal Methods (FMs) [4, 5], and especially Model Checking (MC) [6–8], represents a family of popular techniques which tend to facilitate a low-level representation of systems under study with automata, and which generally provide execution semantics to make the model more understandable. However, these techniques are generally based on a single specific formal foundation often suitable to represent particular aspects of a system under design [9]. Moreover, a system is generally composed of several

components defined by various specifications given from everal points of view, which makes their design really tedious. As a consequence, the use of several techniques, tools, notations and formalisms is required to cover a good range of requirements. Engineers are thus enforced to model the same system over and over again, which is expensive and error-prone. Many attempts have been made to integrate several FMs inside a same framework [10, 11] in order to take advantages of their strengths and reduce their weaknesses. In spite of that, the deep problem related to the trade off between speed, accuracy and level of abstraction has not been fully resolved. For example, representing time in the processes of modelling and checking timed systems is always a tough task. An untimed model is generally derived from a timed system [12], but designing a timed system by an untimed model forces to explore behaviours which may not have an interpretation in the real world. Conversely, representing time with accuracy makes the V&V processes heavier because of the growing size of the model [13, 14], and even unreachable in some cases [13, 15]. FMs then need to impose strong constraints to ensure that the models can be verified in finite time. In fact, Model checking techniques

<sup>1</sup>LIS, Aix Marseille Univ, Université de Toulon, CNRS, LIS, Marseille, France

### Corresponding author:

Dr. Aznam Yacoub - Aix Marseille Université - Campus de Saint Jerome - Bat. Polytech - 52 Av. Escadrille Normandie Niemen - 13397 Marseille Cedex 20

Email: aznam.yacoub@lis-lab.fr

and tools (PROMELA, Symbolic Model Checking, etc.) deal with finite, explicit or symbolic, states models to generate and explore all possible paths and to check formally the system properties and assertions [16, 17]. A system with timed behavioural constraints may then be interpreted as refinement of a system without timed constraints. The reason is that at first glance time may be seen as an additional variable in the specifications of the model; this is a misinterpretation. Taking into account the time basis to describe behaviours leads a fortiori to the appearance of new behaviours that do not belong to the untimed specifications (paths to explore from finite state machines).

For instance, consider model checking applied to digital circuits. It is well known that verifications, such as hold violation, flip-flop set up, etc., are based on models in which states are piecewise constant (0 or 1). However, Hamri et al. [18] proposed timed models to design digital circuits based on the boolean algebra and Generalized Discrete Event Specification (GDEVS) [19] formalism showing the appearance of new behaviours (piecewise continuous state functions and new outputs at times when different input signals cross each other) that finite state machines cannot capture. A second example handled in the model checking literature is the Pacman game, as in [20] and [21]. Formal verification of Pacman behaviours is done on an untimed model and on a discretized space. Unfortunately, the proposed formal model for the Pacman game is so abstracted that it does not conform to the final game requirements. For example, the move of entities (pacman and ghosts) depends strongly on time, as shown in [22]. Consequently such paths are uncovered by the formal model.

Modelling and Simulation. On the other Modelling and Simulation (M&S) theory [23, 23] pr an elegant and uniform way to understand and design systems. This theory is based on two main separated activities. First, Modelling is the tas →of making a representation of a system of a software from the point of view of an observer. M. delling answers questions that this observer asks about the system [25]. If this definition meets the one used in V, the main difference is in the intended purpose of this movel. Second, Simulation is then the task of executing be model to generate its behaviour by acting on inputs and parameters of this model [23]. As a consequence, a sin lation model is made for validating a particular set of behaviours of a system, while a verification model tries to expose the entire set of computation paths of this system (or at least, the set represented by the model). A simulation model can thus be more complex than a verification model, meaning it can encompass more computational details. A simulation model is thus used when [26, 27]:

- it is impossible or extremely expensive to observe certain processes in the reality, or to interact directly with them;

- the real system has some level of complexity, interaction or interdependence between various components, or pure size that makes it difficult to grasp in its entirety;

- there is no simple analytic model or it is impossible or extremely expensive to validate the mathematical model describing the system.

This assumption introduces the main difference with verification model and simulation model: while a verification model must be as simple as possible in order to be able to generate the entire stateset [28] and to perform verification, a simulation model can deal with the complexity of the interactions between the components by representing what the designer knows about the system, what he is seeing when he stimulates the system, without being constrained by any computational considerations or restrictions. This have an impact on the formalisms used for making simulation models. It is indeed possible to introduce two levels of models: a conceptual model which is the representation of the system under study, and the computerized model (called *simulation* model) [2] which is the realization of the conceptual model. This separation gives its power to simulation formalisms. Indeed, for example, the Discrete Event System Specifications (DEVS) [23] are an algebra formalism to explicitly represent Discrete-Event Systems (DES), with all considerations about time and lata, the semantics of the abstract simulator gives interpretation to a DEVS model. As a consequence, a DEVS model is then more expressive than an untimed model of a DES. In other words, some verifications and validations can be performed on the conceptual model while some other properties can be rified and alidated using the simulation model.

wever if the ability to separate conceptual model and simulation model is a strength, it is also a weakness. The power of the simulation-based verification comes from the fact that simulation is like an empirical experiment. We mean that the simulation is efficient because the played seenarios are well targeted, forcing designers to get more knowledge about the system under study. While the goal of FV techniques is to systematically explore all the behaviours of a system, simulation-based techniques focus on interesting cases. Nevertheless, this also means that simulation-based verification strongly depends on the played scenarios, meaning there is no guarantee that the verification is fully done, like in formal-based verification. In the same manner, simulation is done under a specific set of conditions called the Experimental Frame (EF) [23]. This set of constraints is the same than those under the real system is observed. This adds two difficulties:

- If the hypothesis are incorrect, there is no guarantee about the simulation model, meaning the simulation model could only behave well under the EF, and not under all the non-observed conditions;

- The validation strongly depends on the quality of the implementation; this means the simulation model must be verified and validated against the conceptual model, whose the knowledge depend on the known EF.

Understanding and specifying the context and the EF becomes therefore another challenge [29] in the application of M&S theory. This does not mean the entire state space cannot be checked as with formal verification, but it would be probably more costly; and, efficiency of a simulation model can only be evaluated by comparing its outputs with those of the real system for specific inputs. Note that because simulation is evaluated under specific EF, this enforces the notion of determinism; in other words, for the same set

of inputs, the model must generate the same behaviour and the same outputs. This determinism is both a strength and a weakness: from the M&S point of view, this forces again modeller to have precise knowledges about the system; from the FV point of view, this forces the modeller to complexify the model, meaning the model will not focus only on interesting aspects and will encompass irrelevant computational details. Table 1 summarizes the advantages and drawbacks of both formal-based and simulation-based techniques.

### 1.2 Related work

In order to improve these existing methodologies, some works have been intensively done the last decades on new model-checking algorithms for verification of timed and hybrid models [30, 31], stochastic models [32], improving verification and validation of simulation models [33-35]. Many methodologies combining formal-based verification and simulation like assertion-based approaches [36] have also been proposed. Godefroid [37] says that "model checking can be combined with testing to define a dynamic form of software model checking based on systematic testing", confirming that static and dynamic approaches can be both used for Verification and Validation. Goldberg [38] admits that simulation and formal verification are complementary. The author states that if formal verification proves that a model holds property for all points of a space, the main problem is its unscability. He states also that simulation probes the search space at a subset of points, and "works surprisingly well even though the say of test points (further referred to as the test (a) comprise a negligible part of the search space". In fact, combining simulation and verification is an aspect which is included j the definition of model checking [16]. The MC community proposes "testing", "emulation" and "simulation" as a way for analyzing generated counterex mples. In this context, "simulation" (or more precisely execution, or animation of specifications [39]) is stalar torun a path of the reachability graph. However, by definition, simulation is "executing a model to generate its behaviour over the time" [24], by acting on inputs and parameters of the model. Errors are determine by finding differences between the simulator output and be output described in the specifications over the type. Then, executing a graph of an untimed model is not really a simulation (in the meaning of the M&S theory) while execution misses two important aspects: the time and the experimental frame.

That is why many other techniques that combines Simulation and Formal Methods have been proposed. Among them, we find methodologies based on morphisms and transformations of models, and techniques that build new formalisms from several other formalisms used in different disciplines. For instance, Abdulhameed et al. [40] propose a methodology to verify and validate SysML specifications by successively translating them into SystemC and UPPAAL models, using a Model-Driven Engineering (MDE) approach. The SystemC model is then simulated for validation purposes, while the UPPAAL model is used for verification purposes. The described methodology was applied on a model of controls of traffic lights. This type of approach is very interesting because they can reach

the strength of formal verification and simulation from a common high level specification language. However, the limits of this approach come from the limits of the transformations from SystemC to UPPAAL. Timed Automata (TA) impose some restrictions on time relations and data types. This means that there is no proof that any SysML models can be translated into a SystemC model and an UPPAAL model. In the same manner, Zeigler et al. [41–43] propose to use system morphisms to transform DEVS (resp. model-checking) models into model-checking (resp. DEVS) models.

Dacharry et al. [44] propose another design methodology for control systems by linking simulation using DEVS and formal verification using TA. The high-level specifications are expressed using TA, while the design of the ontrol implementation is described using DEVS formalism By finding a refinement between the implementation and the specification (i.e. by proving the DEVS model conforms with the TA model), simulation can then be used for validating the implementation. Moreover a DEVS model expressive and enforces fever constituints about data and time relations. A DEVS model is thus closer to the real system than a verification model. New rthless, this approach supposes that it is postable to translate any DEVS models into equivalent TA nodes, and as the authors stated, this is . Second, because a fully automatic translation not possib. TA to DEV. is not possible, this means that designers fron must have knowledge of two formalisms to achieve the best of combined simulation and model checking.

He [9] proposes to build a new formalism integrating two other formalisms. On the one hand, PZNets can be seen as an extension of Petri Nets, by adding function definition capabilities; one the other hand, it can be also seen as an extension of Z notations, by adding a new operational semantics with explicit control flow structures. The main advantage of such an approach is that the various aspects of a system can be modelled using a unified formal model which can benefit from a rich set of analysis techniques. Indeed, a PZNet model remains a Petri Net model, meaning that it can be simulated. Moreover, a PZNet model can be analyzed using the Z proof techniques thanks to the defined transformation rules. Thus, a PZNet is suitable for both data and process reasoning.

We proposed [45, 46] to go further in this way and to explore how combining Model-Checking and Simulation for improving V&V by introducing the semantics of simulation formalisms into verification formalisms (at the difference with PZNets which adds Z notations to Petri Nets). In this way, we achieve different goals:

- Building a unique formalism that allows designing accurate representations of software which before were not fully representable with only one formalism;

- Keep a model with a clear syntax that focuses on the properties which one wants to verify, without losing the timed semantics;

- Keep a separation between the conceptual model (which is the verification model) and the simulation model (which is the computerized model);

Many advantages arise from such a methodology:

| Table 1. Advantages and Dr. | awbacks of Formal- and Simulation-based V&V  |                                               |

|-----------------------------|----------------------------------------------|-----------------------------------------------|

|                             | Advantages                                   | Drawbacks                                     |

|                             | Explore the full statespace                  | Related to statespace explosion problem       |

| Formal-based V&V            | Non-deterministic model                      | (timed models are hard)                       |

| Formar-based V&V            | Simple analytic model: model is focused on   | Related to decidability problem : models      |

|                             | what to be verified/validated                | must be finite or symbolically finite         |

|                             | Separation between conceptual and imple-     |                                               |

|                             | mented model                                 |                                               |

|                             | Interoperability between simulation for-     |                                               |

|                             | malisms, and between simulators is easier    | Strongly depends on EF and scenarios          |

|                             | (thanks to the separation between the mod-   | No guarantee that the V&V is fully done       |

| Simulation-based V&V        | els)                                         | V&V depends on the quality of the comput-     |

| Simulation-based v & v      | Exsisting universal formalism and frame-     | erized model (the computerized model must     |

|                             | work for modelling a large set of systems    | also be verified and validated against the    |

|                             | Deterministic model (well-known specifica-   | conceptual model)                             |

|                             | tions)                                       |                                               |

|                             | Non-related to complexity (time, infinite    |                                               |

|                             | data, computations, etc.)                    |                                               |

|                             | Separation between conceptual and imple-     |                                               |

| Combined V&V                | mented model                                 |                                               |

|                             | Structural static properties can be formally | Cannot represent all existing systems (the    |

|                             | checking exploring the entire statespace     | model remains symbollically finite)           |

|                             | Behavioural dynamic properties can be        | Remains strongly dependant on experts,        |

|                             | checked using simulation                     | requirements, stenatios (parameter space      |

|                             | Hierarchical and modular constructions of    | can be fully explored, but it would take huge |

|                             | the models make easier the analysis          | an ount of time)                              |

|                             | Makes easier the interoperability be ween    |                                               |

Table 1. Advantages and Drawbacks of Formal- and Simulation-based V&V

• A robust V&V of models and systems can be achieved through a method based on the strengths of formal verification and simulation. In this approach, simulation and formal verification complete each other in the V&V processes. Model-Checking is used for verifying and validating some static properties like bounding values, structural deadfocks etc. in an untimed mode, while simulation is used for checking dynamic properties, behavioural deadlocks etc. in a timed mode.

existing tools

- Simulation formalisms can benefit from a clear syntax that makes earlier the implementation of computerized

- Unlike timed formal verification, the size of the statespace is subdued, and the expressiveness of the timed model is still preserved;

- What which is checked, verified and validated is more clear: conceptual model, computerized model and real software are clearly separated in this approach.

- The hierarchical construction reduces the complexity

of the formal model, and the relevant parameter space

is better targeted (analysis of the relevent properties

makes easier the choice of the subspace in which the

model is tested).

As a result of our work is born the Discrete-Event PROMELA (DEv-PROMELA) formalism [47] which can be seen as a new specification formalism thanks to the combination of DEVS and Process MEta LAnguage (PROMELA) [48] formalisms presented in section 1.3 and section 1.4.

### 1.3 PROMELA Concepts

PROMELA [48] is a formal verifiable language which allows the specification of concurrent systems and concurrent protocols. The model-checker SPIN makes possible of the validation of properties expressed in Linear Temporal Logic (LTL). We briefly introduces there the main concepts behind PROMELA.

**PROMELA primitives.** A PROMELA system [28] relies on three main types of objects: *processes*, *data objects* and *messages*.

The components of the system are modelled by a finite set of instances of processes. The latter can communicate with each other thanks to different mechanisms such as buffered messages, shared global variables or rendez-vous handshakes. Each process is a finite set of guarded or labelled commands called instructions. Each instruction is sequentially executed by each process in an either synchronous or interleaved asynchronous manner. In other words, at any time  $t_i$ , only one instruction is performed by one of the processes, without any assumptions about duration of the execution or timed events. Note that a set of instructions can be labelled as an atomic instruction: in this case, these instructions are considered as a unique instruction. Processes can also be prioritized, meaning that a process with a higher priority will always execute its instructions before other processes (it is interesting to note that the semantics of priority has changed: old PROMELA specifications provided a way to define a ratio between processes, meaning that, for instance, a 10-priority process was 10 times more likely to execute before others).

**ALGORITHM 1:** A simple example of PROMELA program.

```

1: int z = 1;

2:

3: active proctype A {

4:

int x = 2, y = 2:

5:

if

6:

:: (x == 2) \to x = 3;

y = 2 \to y = 4;

y = (y = 4) \rightarrow z = 0;

8:

9:

fi;

10: }

11:

12: active proctype B {

int x=2, y;

13:

14:

do

15:

:: (z == 1) \to x = 2;

16:

:: (x == 2) \rightarrow y = 4;

y = (y = 4) \rightarrow z = 0;

17:

18:

od;

19: }

20:

21: Itl \{[](z == 1); \}

```

Syntactically, a *process* is defined by a proctype block of instructions, as given in Program 1.

Instructions are divided into two categories:

- Statements that modify the state of the model ly acting on variables: assignments and communication statements. Assignments are always enabled, meaning there can always be executed, while communication statements can be blocking, depending on the size of the involved buffers;

- Statements that act on the flow: selection statements which choose the next tate and no different branches regarding a guar of many guards are satisfied, one of them is randomly selected. For instance, in 1, if x == 2x and y == 2, both 1.6 and 1.7 are enabled. This consequents to two active paths in the verification graph of no statement can be satisfied, the control-flow is blocked, meaning there is no next state in the reachability graph.

PROMELA data are represented by classic variables, with a type and an identifier. The type gives the finite size of the variable (Table 2). It can be either scalar values, combinations of scalar values (structs), or finite arrays of scalar and/or structs. Variables can be local, meaning there are defined only in the scope of the process that declares them, or global, meaning they are shared by all the processes.

Table 2. A list of PROMELA basic datatypes.

| Type              | Size (bits) | Value Range                          |

|-------------------|-------------|--------------------------------------|

| bit, bool         | 1           | [0; 1]                               |

| byte              | 8           | [0; 255]                             |

| mtype (constants) | 8           | [0; 255]                             |

| short             | 16          | $[-2^{15}; 2^{15} - 1]$              |

| int               | 32          | $\left[ -2^{31}; 2^{31} - 1 \right]$ |

Semantics of PROMELA. The semantics of a PROMELA model is given by the verification engine [28, 49]. Each proctype defines a finite state automaton  $A = (S, T, L, s_0, F_A)$  where:

- S is the set of states that correspond to the possible control points inside the proctype block;

- T is the transition system that defines the control flow;

- L is the transition label function that links each transition to a statement that defines the executability and the effect;

- F is the set of final states which are defined for endstate, accept-state and progress-state.

More operationally, a PROMELA process is a tuple

P = < pid, lvars, lstates, initial, curstate, trans

### where:

- pid is a positive value which identify the process,

- lvars is a finite set of local variables {(name, scope, domain, inival curvul);

- lstates ⊆ INT, which defines the identifiers of the local states of the proces; lstates hold no information;

- initial is the initial state of the process such that

$$cyrstate = initial \implies \\ \forall v \in lvars, v.curval = v.inival;$$

- curstate is the current state of the process.

- trans is a the finite set of transitions  $\{(tr\_id, source, target, cond, effect, prty, rv)\}$  where  $(source, target) \in lstates \times lstates$ .

Then, to define a whole PROMELA program, the concept of *System state* is introduced. A system state is a tuple

```

SS = < gvars, procs, chans, exclusive, handshake, timeout, else, slutter >

```

where, in particularly,

- gvars is a finite set of global variables {(name, scope, domain, inival, curval)};

- procs is the finite set of processes;

- chans is the finite set of channels.

The semantics engine (Algorithm 2) gives then the meaning of a PROMELA program. Given a current system state s, the semantics engine takes randomly one executable transition from any executable transitions among all the processes. Given a selected couple (p,t), the engine computes the effect of the transition on the current state. If the statement is not a synchronization statement, the engine modifies the current system state and the current state of the selected process. Otherwise, the algorithm tries to find the process that must fulfill the synchronization. If one is found, both processes are updated and the current global state is changed. Otherwise, the system is blocked.

Then, we can consider a PROMELA program also as a finite state automaton in which the set of states is the cartesian product of each process' set of states, and the

### **ALGORITHM 2:** PROMELA Semantics Engine [48]

1: while there is at least one executable transition from the current global state s

```

2:

3: for one (p,t) \in procs \times p.trans {

4:

s' = apply(t.effect, s)

5:

if handshake == 0

6:

7:

s = s'

8:

p.currstate = t.target

9:

}

10:

else

11:

E' = executable(s')

12:

for one (p',t') \in E' {

13:

s = apply(t'.effect, s')

14:

15:

p.currstate = t.target

p'.currstate = t'.target

16:

17:

18:

handshake = 0

19:

20: }

```

transition system is a composition of each transition system of each process. We mean that, for two global state s and s', it exists a transition between them only if it exists a local transition that affects one of the local states that composes s and gives its equivalent component in s'.

### 1.4 DEVS Concepts

As introduced previously, DEVS is an algebraic formalism which allows discrete-event representations of system. In this section, we recall important concepts about Classic DEVS [24].

DEVS primitives. Decrete Event Systems (DES) are a specific class of timed systems, whose state changes at various time inclusts, eppending on instant occurrences of events. Thus, a DES evolves along the events that it emits or consumes. To model such systems and their analysis, Zeigler et al [23] introduced the DEVS formalism, which can be seen as a generalization of the Moore Machine formalism by associating each state with a lifespan. The Classic DEVS thus relies on the following notions:

- Each state is associated with a real number called lifespan. This real number can take its value on [0; +∞]. When the lifetime of a state has expired, the system emits an output and changes its current state according to the transition table;

- When an input is consumed, the state of the system changes according to the transition table, regardless of the current lifetime of the current state;

- As a result of the previous point, transitions can be characterized as internal or external transitions. Internal transitions model autonomous behaviours while external transitions correspond to reactions to any external events;

- Events are well-dated and can be ordered;

- There is no non-deterministic behaviour. If two events occur at the same time, thus either they are equivalent events  $(e_1 = e_2)$  or they are prioritized;

- The states, input and output trajectories are piecewise segments; the distribution of events can follow any non-linear function, unlike for discrete-time systems in which the time is determined by a linear function of periods;

A DEVS model is divided into small pieces called *DEVS* atomic model, and more complex models called *DEVS* coupled model. A coupled model is a coupling of DEVS atomic or coupled model. Each atomic model deals with events that it receives from the environment, or from other models, in order to change its current state. An atomic model thus encompasses the computational properties of the system. When a transition is enabled, an atomic model con emit an event to the other models which it is coupled with. It is the case, the target models change their respective state according to the emitted event. A coupled mode is thus a way to hierarchically compose complex systems.

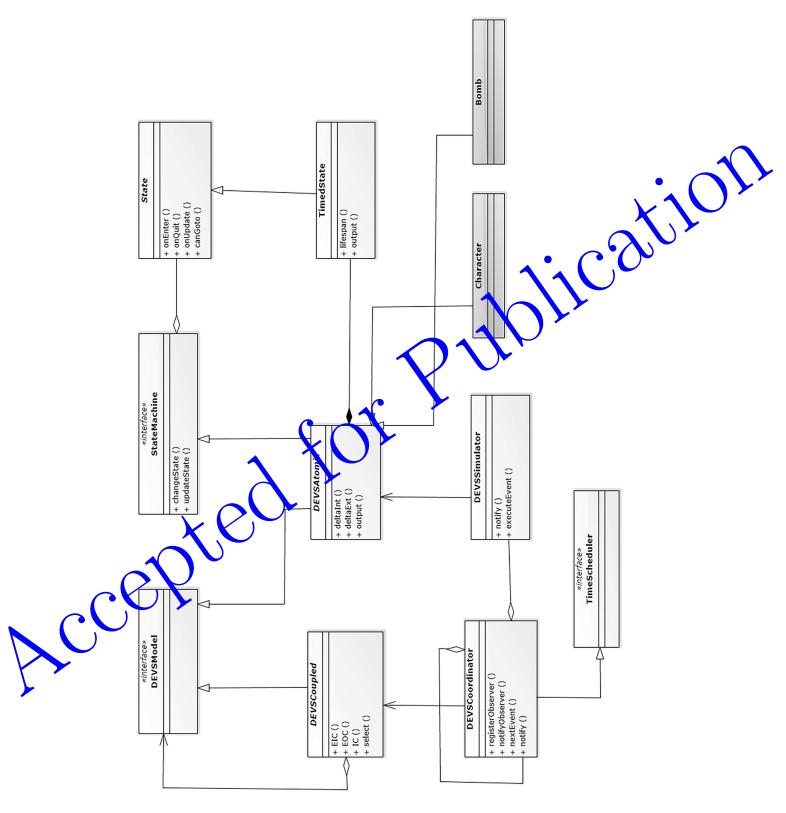

To each model, the DEVS frame work associates either an abstract simulator, or an abstract coordinator in order to build the simulation model. The simulator gives the meaning of an atomic model, while the coordinator sets how the events are exchanged between coupled models. The computerized model is then the concate implementation of simulators and coordinators using a programming language.

Semantics of DEVS. More formally, a DEVS model is thus a coupling of DEVS models. A DEVS atomic model is the smallest simulable unit defined by

$$A = (X, Y, S, \delta_{int}, \delta_{ext}, \lambda, ta)$$

where:

- X is the set of input values;

- Y is the set of output values;

- S is the set of states;

- $\delta_{int}:S \to S$  is the internal transition function;

- $\delta_{ext}: Q \times X \to S$  is the external transition function;

- $\lambda: S \to Y$  is the output function;

- $ta: S \to \mathbb{R}^+$  is the time advance function;

- $Q = \{(s,e) \mid s \in S, \ e \in [0,ta(s)]\}$  is the total state set; e is the time elapsed since the last transition.

Then, a DEVS coupled model is defined by

$$M = (X, Y, M, EIC, EOC, IC, Select)$$

where:

- X is the set of input values;

- Y is the set of output values;

- M is the set of components (atomic or coupled models);

- EIC is the external input coupling that connects external inputs to component inputs;

- EOC is the external output coupling that connects component outputs to external outputs;

- IC is the internal coupling that connects component outputs to component inputs (without direct feedback loops);

Select is the tie-breaking function that chooses the next event from the set of simultaneous events.

The meaning of an atomic DEVS, given by the abstract simulator, can easily be depicted as follows. At any time t, the system is in a state s. If no external event occurs, the system stays in s for time ta(s). If the lifetime expires, meaning the elapsed time e from the last event is equal to ta(s), the system outputs the value  $\lambda(s)$  and changes to the state  $\delta_{int}(s)$ . If an external event x occurs before the expiration time, meaning that the system is in a state q=(s,e) with  $e\leq ta(s)$ , then the system changes its state to  $\delta_{ext}(q,x)$ .

Given a queue of events sorted by date, the simulation algorithm works as follow:

- When a coordinator associated to a coupled model processes an internal event, it dispatches it to its imminent child, ie. the one responsible of this event. The simulator associated to this model executes its transition. If it is a coordinator, the event is processed recursively. Otherwise, if it is a simulator, an output event is emitted to the parent coordinator before changing the state of the corresponding atomic model. When the internal event is consummed and all external events caused by this output processed, the time of the next event is computed by choosing the minimum of the next events of all the children;

- 2. If a coordinator receives an external input event from its parent coordinator, it generates a message to its internal components according to the internal coupling function. Time event are updated.

- If a coordinator receives an external output event from its imminent child, it may generates an external output event to its parent coordinator according to the external coupling function or internal coupling function;

- 4. The algorithm is repeated until the event queue is empty.

Based on these two hymnalisms, we developped DEv-PROMELA presented a this paper as new formalism, and as an illustration of our proposed methodology. The question about the exact posit on of DEv-PROMELA as an extension of FROME A or a subclass of DEVS is not raised in this oper. Section 2 reintroduces DEv-PROMELA and the mandatory key concepts to build a combined formalism both on formal method and simulation in the context of Software Verification and Validation. Unlike previous work, this section shows also that the resulting formalism is usable both by the former checker and the former simulator because of the existance of morphisms that generate equivalent PROMELA specifications and DEVS models from a DEv-PROMELA specification. Through a double bi-simulation relationships, we ensure that DEv-PROMELA models, resulting PROMELA models and resulting DEVS models are equivalent. Then, Section 3 introduces a new unpublished proposed V&V workflow and Software Development Life Cycle (SDLC) using DEv-PROMELA. Indeed, simulation is generally used to develop systems, but we show that it can be combined with formal checking to discover flaws early in a software development. We applied our methodology to develop a video game using DEv-PROMELA and we show

how each step of the SDLC is impacted in our proposed workflow in Section 4. Finally, we discuss about the benefits and drawbacks of our approach and its applicability on more complex software and systems.

### 2 Discrete-Event PROMELA

### 2.1 Overview

Discrete-Event PROMELA (DEv-PROMELA) [47] is an example of formalism that illustrates our methodology. DEv-PROMELA can be seen as an extension of PROMELA for describing discrete-event models, while it adds new abstract primitives [50, 51] to PROMELA, or as a new discrete-event simulation formalism. More than that, DEv-PROMELA is also a sublclass of DEVS [23]. Proof of the exact position of DEv-PROMELA is outside of the scope of this paper. As previously said, DEv-PROMELA is built upon a varification language (with an operational semantics) in which ve add the operational semantics [52, 53] of a simulation language. In other words, the structure of a DFV-PROMELLA model can be fully described/abstracted by PROMELA model (the state-transition graph generated by the semantics of the PROMELA verification angle), while its discrete-event behaviour is described y a D. V. model (the way of going from a state to another given by the semantics of the DEVS abstract sin ulater). As a consequence,

- DEV-PROMELA model can be abstracted to a Prometa model in which the structure is preserved. This means that some qualitative properties like the intrisic existance of a path between two abstract states can be formally checked; time is seen as ordered events and the size of the statespace of models can be subdued (compared to the statespace of a timed model):

- a DEv-PROMELA model can be abstracted to a DEVS model in which the timed behaviour is preserved. This means that some quantitative properties, like properties in which the next state depends on the time elapsed in the current state, can be checked by simulation; time is seen as timed events and discreteevent simulation models can be expressed with a clear syntatic language.

Shorter, DEv-PROMELA is thus a formal language with the syntax of PROMELA. It embbeds both PROMELA and DEVS primitives. The semantics of the simulation model is given by the DEVS abstract simulator.

### 2.2 Syntax of DEv-PROMELA

DEv-PROMELA is then designed as an extension of PROMELA for the modelling of discrete-event systems. However, in order to model the previously described DEVS primitives, new syntactic elements are obviously needed. PROMELA is a deep and interesting specification language with plenty of elements. Thus, we just present in this section the minimal main modifications that will allow the modelling of discrete-event systems.

A new datatype. For representing infinite and unbounded real values, we introduce a new abstract type called **real**. It is useful for modelling time and infinite data. As any other

PROMELA types, real can be used to defined local and global variables.

```

real i, j, k;

```

Real variables can also be used in structures and in arrays, without restriction.

Statements. PROMELA statements define the actions which are done when the system changes its state following a transition. DEv-PROMELA extends them by prefixing each of them with *an event descriptor*, which allows their characterization, i.e. if they are autonomous or reactive statements.

Event descriptors describe the delay between the execution of any previous statement and the prefixed one, or describe an event which will trigger the execution of this statement. Event descriptors are defined as follows:

```

<event stmnt> ::= "[" <timed trans> "]"

<stmnt> | <stmnt>

<timed trans> ::= <clt expr> | <evt

expr> | <clt expr> <op> <evt expr>

<clt expr> ::= "clt:" <real expr>

"->emit:" <evt val>

<evt expr> ::= "evt:" <evt val> [ <op>

<evt expr> ]

<op> ::= "|"

<evt val> ::= <mtype> | "silent"

<real expr> ::= <real> | "infinity" | /*

Any C-function returning a real value */

```

Consider the following examples:

```

[clt: 3.0 → emit:newal a = a + 10;

[evt:newb] b = a - b;

[clt:lifespan(c) → emit:newc | evt:newd] c = c + d;

```

- (1) means that the execution of a = a + 10 is performed 3.0 units of time after the execution of a previous statement. Before executing this statement, an event newa is emitted.

- (2) means that the statement will be triggered only if the even "news" is received.

- (3) means that the statement c = c \* d will be triggered either if the elapsed time between the execution previous statement and this one is equal to the value lifespan(c) (in this case, "newc" will be outputed) or, if the the event "newd" occurs.

The third example shows one of the main characteristics of DEv-PROMELA: a statement can be executed in different manners, with at most one explicit timed descriptor (defined by clt command) and with at most one descriptor per event. Note that the clt command is optional. If it is not defined and there is at least one evt command, we consider the elapsed time before the execution of the statement is equal to  $\infty$ . For convenience, if there is no event descriptor (no clt command nor evt command), the statement is interpreted as if it is prefixed by [clt:  $0.0 \rightarrow \text{emit:silent}$ ]. The statement is executed without any delay by emitting the default **silent** event. The silent event is an event which does

not cause any explicit change in the system, but defined in order to conform to the DEVS formalism.

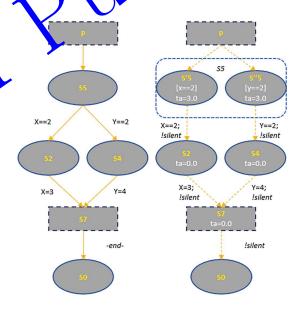

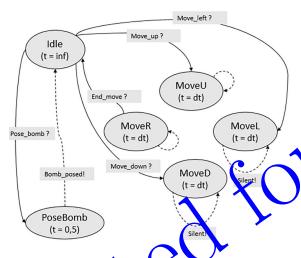

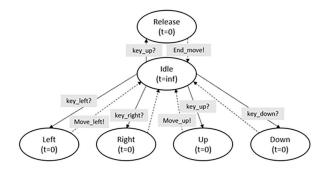

Selection construct. The selection construct is a control-flow construct that helps to define the structure of the automaton corresponding to the PROMELA program. The original construct has a unique start and stop state. Each option sequence defines an outgoing transition from the start state to the stop state. Thus, the end of each option sequence leads to the end state that follows the construct. Consider the example given in Algorithm 3. The PROMELA resulting structure is composed by three states per path, as shown in Figure 1. When entering the selection construct, the process evaluates each guard, leading to an intermediate state, before executing the option. This mechanism allows PROMELA to separate evaluation of guard and outgoing instructions. If two options are evaluated to true, both paths can be executed in a non-deterministic manner.

### ALGORITHM 3: PROMELA conditional structure

```

1: if

2: :: (x == 2) \rightarrow x = 3;

3: :: (y == 2) \rightarrow y = 4;

4: fi:

```

**Figure 1.** Structure generated by Algorithm 3 (on the left) and Algorithm 4 (on the right).

In a DEv-PROMELA model, such a construct defines transitions between a set of *equivalent* states. The meaning is that, whatever the state for which x=2, only the transition defined by the first option is defined (except for the state (x=2,y=2)). This transition leads to a state for which x=3. In this case, this means that each option of the construct describes a set of source states verifying at least the guard of the option. Thus, like for assignments, each DEv-PROMELA option is prefixed by an event descriptor. Then, a DEv-PROMELA version of Algorithm 3 is given in Algorithm 4.

### ALGORITHM 4: DEv-PROMELA conditional structure.

```

if

1:

:: [clt: 3.0 \rightarrow emit:silent]

2:

(x == 2) \rightarrow [clt: 0.0 \rightarrow emit:newx] x = 3;

:: [clt: 1.3 \rightarrow emit: silent] (y == 2) \rightarrow

y = 4;

fi:

4:

```

Note that the event descriptor can be placed before the control structure. In this case, this means that all evaluation of each guard will occur after the same delay.

But what happens if multiple guards are verified? Traditional PROMELA allows non-deterministic behaviours, because the model-checker will systematically explore all possibilities. Thus, for a source state, multiple outgoing transitions can exist. Still, a discrete-event simulation model is deterministic by definition. This could be seen as a restriction, but in fact, it forces designers to fully specify the modelled system. Indeed, what does the system actually do if x = 2 and y = 2? DEv-PROMELA considers that the options are ordered by time then by order. For example, in Algorithm 4, only the second option is executed. If the time was the same for both options, the first one would be executed.

Repetition construct. The repetetion construct allows the definition of loops. The structure is likely similar to the to a break statement leads to the end of the structure. As in the case of a conditional structure, the option carbon refixe by an event descriptor.

### **ALGORITHM 5:** DEv-PROMELA loo structure.

```

1:

do

2:

:newx] (x == 3) \rightarrow

wit:newy] ( y == 2 )

ightarrow

```

Consider Algorithm 5. If the program is in a state (x = $3, y \neq 1$ ), the first transition will be triggered after 3.0 units of time, leading to a new state (x = 3, y = 2). The next instruction y == 2 is then executed after a delay of 1.3 units of time.

Process priority. Priority between processes is another thing that we need to be able to define. Indeed, if two events occur at the same time, we need to know what event must be processed first. This corresponds to the select tie-breaking function seen previously. For that, DEv-PROMELA defines a process descriptor using the following grammar:

The semantics of priority will be defined in the next section.

Clock and timeout. The last syntactic element concerns time handling. PROMELA defines a timeout keyword used as an escape for a blocked system (i.e. a system for which there is no more enabled statement), for example when a system has no valid option to progress through a selection construct. In DEv-PROMELA, such a case means that the system is not well specified. In such a case, simulation cannot be performed and will return an error.

Each process is also associated to a virtual local clock which measures the elapsed time since the last event. DEv-PROMELA allows transitions depending on the elpased time. Two convenient instructions, getElapsedTime and getCurrentDate, enable access to this clock valuation.

### Meaning of DEv-PROMELA 2.3

DEv-PROMELA primitives. To keep the equivalence between PROMELA, DEVS and DEv-PROMELA, we associate for each DEv-PROMELA proctype block a DEv-PROMELA atomic process. Each atomic proce is coupled with the other processes that compose the specifications. The whole system is then viewed as a DEv-PROMELA coupled program. Programs car be oupled to make a more complex program or interest with the environment.

Semantics of a DEV PROMELA program. Formally, a DEv-PROMELA program  $P_n$  is a transition system T =where  $\hat{S}$  is the distersion product of the set of states of ch pro ess, he see of global variables and channels that compose the program,  $\Lambda$  is the set of all statements and  $\rightarrow$  the set of the nsitions. Consider a program Pr at time t and two selection construct, except that the end of each option leads states  $s = (s_{p_i}, s_{q_j}, ...)$  and  $s' = (s'_{p_i}, s'_{q_j}, ...)$ . Then,  $s \xrightarrow{l} s'$  back to the start of the structure. Only the option associated with  $l \in \Lambda$  if it exists a transition from  $s_{p_i}$  to  $s'_{p_i}$ , from  $s_{q_j}$ to  $s'_{q_i}$ , ... and if it does not exist any other transition which can be triggered before the date t. In other words, the next event of Pr is the minimum value of all the next events of each process and external events. This definition comes from the fact that a DEv-PROMELA program can be simulated by a DEv-PROMELA atomic process. The demonstration is similar to the closure under coupling property of DEVS.

> Semantics of a DEv-PROMELA process. A DEv-PROMELA process P with a set of statements L is an automaton

$$T = (S_{\tau}, E, \delta_i, \delta_e, s_0, F)$$

where

- $S_{\tau} = \{s_i = (t_s, i, l_1, ..., l_m, ... \in \mathbb{N} \times \prod_{i=1}^m L_i \times \prod_{j=1}^n G_j \times \prod_{k=1}^o C_k)\}$  is the set of states. i is the identifier of the state related to the statement l which defines it; the sets  $L_i$  (resp.  $G_i$ ) are the sets of values of each local (resp. global) variable  $l_i$  (resp.  $q_i$ );

- E is the set of events; E contains at least the silent event denoted  $\epsilon$ ;

- $\delta_i: Q_f \to Q_0 \times E$  is the internal transition partial function;

- $\delta_e:Q\times E\to Q$  is the external transition partial function;

- $s_0$  is the initial state;

- F is the set of final states.

Moreover, we define:

- $ta: \begin{cases} S_{\tau} \to \mathbb{R}^+ \\ s \mapsto t_s \end{cases}$  is the state lifetime function; the lifetime of each state is given by the delay before executing the next statement in the specifications;

- $Q = \{q = (s, dt), \forall s \in S_{\tau}\}$  such that  $0 \le dt \le ta(s)$  is the set of total states; dt denotes the time elapsed in the state s:

- $\begin{array}{l} \text{-} \ Q_0 = \{q = (s,0), \forall s \in S_\tau\} \subset Q; \\ \text{-} \ Q_f = \{q = (s,ta(s)), \forall s \in S_\tau\} \subset Q. \end{array}$

Consider a DEv-PROMELA process P in a state s at time t, and the next statement l with its event descriptor. We can admit the process P is in fact in a state q=(s,t) (if t denotes the elapsed time since the last event). If l denotes an internal transition and if t=ta(s), then the statement l is enabled. The event associated with the transition is emitted to all the other processes composing the program, before the transition is triggered, and the next event for the process P is defined by  $\cdot$

$$d_{e'} = getCurrentDate + ta(s')$$

with  $((s',0),e')=\delta_i(s)$ . If l denotes an external transition on an event e, then the transition is triggered only if the process receives the event e. In this case, denote t the date of the event e. The next state is given by  $q'=\delta_e(q,e)$  with q'=(s',0). If  $\delta_e$  is not syntactically defined for (s,e), then the next state is given by q'=(s,dt) and  $ta(s)=t_s$  where dt is the elpased time from the previous event.

# 2.4 Relations between DEv-PROMELA and DEVS

The main goal of DEv-PROMELA is to provide another way to enhance modelling, verification and validation of discretevent systems by using simulation and model-cecking. To do that, we must demonstrate that a DEv-PROMELA model can be simulated and verified. The first-klation can be easily demonstrated by showing that, for a given DEv-PROMELA model, it exists a DEVS model that a mulates it.

**Proposition 1.** A DE PROMELA atomic process P is a DEVS atomic model.

This demonstration is relatively easy, thanks to the construction of DEv-Promella. Consider a DEv-Promella process  $F = (S_e, E, \delta_e, \delta_e, s_0, F)$  and a DEVS atomic model  $A \neq (X, Y, S, \delta_{int}, \delta_{ext}, \lambda, ta)$ . P will define the same system as A if and only if :

- $S_{\tau} = S$ , both models have the same state space;

- X ⊆ E and Y ⊆ E; the sets of inputs and outputs are subsets of the set of events;

- 3. given s and s' two states such that  $s' = \delta_{int}(s)$  and  $y = \lambda(s)$ ; then, it exists  $s_{\tau}$  and  $s'_{\tau}$  such that  $((s'_{\tau}, 0), y) = \delta_i((s_{\tau}, ta(s_{\tau})))$  and  $ta(s) = ta(s_{\tau})$ ;

- 4. given s and s' two states, and x an input such that  $\delta_{ext}(s,x) = s'$ ; then it exists  $s_{\tau}$  and  $s'_{\tau}$  such that  $s'_{\tau} = \delta_{e}(s_{\tau},x)$ ;

**Proof.** Considering a DEVS atomic model built upon a DEv-PROMELA process model, in which  $X=E,\,Y=E,$  and  $S=S_{\tau}.$  We define  $\delta_{int}$  and  $\lambda$  such that:

• if  $ta(s) \neq \infty$  and  $\delta_i(q) = (q',e)$  such that q = (s,ta(s)) and q' = (s',0), then  $\delta_{int}(s) = s'$  and  $\lambda(s) = e$ .

• if  $ta(s) = \infty$ ,  $\delta_{int}(s) = s$  and  $\lambda(s) = \emptyset$ . s is a passive state, then this transition will never be enabled.

We define  $\delta_{ext}$  as follows:

- if  $\delta_e(q,e)=q'$  with q=(s,dt) and q'=(s',dt'), then  $\delta_{ext}(q,e)=s'$ ;

- if q=q' and  $ta(s) \neq \infty$ , then ta(s')=ta(s)-dt and q'=(s',0). This condition ensures that  $\delta_{ext}$  is defined for all  $(q,e) \in Q \times X$  and time is preserved.

Then, we can show that A simulates P. Considering the transition system  $< S', \Lambda, \rightarrow >$  where

- $S' = S_{\tau} \cup S$ ;

- $\Lambda = (X \cup E) \times (Y \cup E);$

- $\rightarrow = Im(\delta_i) \cup Im(\delta_{int}) \cup Im(\delta_e) \cup Im(\delta_{ext});$

where  $\cup$  denotes the disjoint union operator. Therefore, A simulates P if there is a simulation  $R = S' \times S'$  such that for all  $(p,q) \in R$  and  $l = (x,y) \in \Lambda$ , if

$$p - p'$$

then

$$q \stackrel{l}{\longrightarrow} q'$$

Herever,  $p \stackrel{l}{\rightarrow} p$  only  $^{\mathbf{c}}$

- 1.  $(x,y) = \delta_i(p)$ , meaning that p' is reached by an internal transition that outputs y. By construction, we know that it exists  $(q,q') \in \to$  such that  $q' = \delta_{int}(q)$  and  $y = \lambda(q)$ . Moreover, ta(p) = ta(q) and ta(p') = ta(q') by construction.

- 2.  $p' = \delta_{int}(p)$  and  $y = \lambda(p)$ , meaning that p' is reached by an internal transition that outputs y. By construction, we know that it exists  $(q, q') \in \rightarrow$  such that  $(q', y) = \delta_i(q)$ . Moreover, ta(p) = ta(q) and ta(p') = ta(q') by construction.

- 3.  $p' = \delta_e(p, x)$ , meaning that p' is reached by an external transition that consumes x. By construction, we know that it exists  $(q, q') \in \rightarrow$  such that  $q' = \delta_{ext}(q, x)$ . Moreover, ta(p) = ta(q) and ta(p') = ta(q') by construction.

- 4.  $p' = \delta_{ext}(p,x)$ , meaning that p' is reached by an external transition that consumes x. By construction, we know that it exists  $(q,q') \in \rightarrow$  such that  $q' = \delta_e(q,x)$ . Moreover, ta(p) = ta(q) and ta(p') = ta(q') by construction.

Thus, A simulates P. Symetrically, we can show that for all  $(p', q') \in R$ , if

$$q \stackrel{l}{\rightarrow} q'$$

then

$$p \stackrel{l}{\to} p$$

Thus, P simulates A, meaning P and A are bisimilar.

We can then build a DEVS atomic model that simulates exactly the behaviour of a DEv-PROMELA process.

**Proposition 2.** A DEv-PROMELA program  $P_r$  is a DEVS atomic model.

**Proof.** Given a DEv-PROMELA program  $P_r$  with nprocesses  $P_1$  to  $P_n$ . Given EVENT, a convenience function such that  $EVENT(P_n)$  is the set of events of  $P_n$ . Then, we can define a DEVS atomic model  $A = (X, Y, S, \delta_{int}, \delta_{ext}, \lambda, ta)$  which simulates the DEv-PROMELA program:

- 1.  $S_{\tau} = \bigcup_{i=1}^{n} S_i \times \prod_{j=1}^{n} G_j \times \prod_{k=1}^{o} C_k$ , where  $S_i$  are the sets of the states of each process,  $G_j$  the sets of the values of the global variables, and  $C_k$  the sets of the values of the channels;

- 2.  $X \subseteq \bigcup^n EVENT(P_n)$  and  $Y \subseteq \bigcup^n EVENT(P_n)$ ; the sets of inputs and outputs are subsets of the set of

- 3.  $\delta_{int}: S_{\tau} \to S_{\tau}$ . Given  $s = (s_1, s_2, ...)$  and s' = $(s'_1,...)$  and  $s'' = (..., s'_2,...)$  in  $S_\tau$ . Then:

- if  $\delta_{i_1}(s_1, ta(s_1)) = (s'_1, 0, e)$  where  $\delta_{i_1}$  is the internal transition function of the process 1, then  $\delta_i(s) = s'$ ;

- if  $\delta_{int}(s) = s'$  and  $\lambda_1(s_1) = e$ , and  $\delta_{e_2}(s_2, dt, e) = (s'_2, dt'), \text{ then } \delta_{int}(s') = s''$ and ta(s') = 0; this case describes the internal coupling of DEv-PROMELA processes;

- 4.  $ta: S_{\tau} \to \mathbb{R}$ .  $s = (s_1, s_2, ...)$  and  $s' = (s'_1, ...)$ , then:

- if s is the initial state, ta(s) = $min(ta(s_1),...,ta(s_n));$

- $s' = \delta_{int}(s),$ then ta(s') = $min(ta(s_1'), ta(s_2) - ta(s_1), ..., ta(s_n)$  $ta(s_1)$ ;

- if  $s' = \delta_{ext}(q, e)$  and q = (s, dt), then ta(s') $min(ta(s'_1), ta(s_2) - dt, ..., ta(s_t) - dt))$

- 5.  $\delta_{ext}: Q \times X \to S_{\tau}$ ; Given  $s = (s_1, s_2, ...)$   $(s'_1, ...)$  and  $s'' = (..., s'_2, ...)$  in  $S_{\tau}$ . If  $\delta_{e_1}(s_1, s_2, ...)$   $(s'_1, dt')$ , then  $\delta_{ext}(s, e) = s'$ ; 6. given  $s = (s_1, ...)$ ,  $\lambda(s) = y$  if  $\lambda(s_1) = y$ ;

We must show that A simulates  $P_r$ . We denote by  $STATESPACE(P_r)$  the total statespace of the DEv-PROMELA program  $P_r$ . If A) simulates  $P_r$ , this means that for each (p,p') is  $STATESPACE(P_r)$  such that  $p \to p'$ , it exists  $(q,q) \in X$ , such that it exists an internal or an external reasition to to from q to q'. But,  $p \to p'$  if:

- $p = (s_{p_i}, ...), p' = (s_{p'_i}, ...)$  and  $\rightarrow = (\delta_{i_p}, ...)$  such that  $(s_{p'_i}, y) = \delta_i(s_{p_i});$  by construction, we know that it exists  $\delta_{int}(q) = q'$  and  $y = \lambda(q)$  that corresponds to the transition  $\delta_i(s_{p_i})$ . Moreover, ta(p) = ta(q)and ta(p') = ta(q'). Indeed, the next event in  $P_r$  is generated by the minimum value of all the future events. And by definition, ta(q') = $min(ta(s'_1), ta(s_2) - ta(s_1), ..., ta(s_n) - ta(s_1)).$

- 2.  $p = (s_{p_i}, ...), p' = (s_{p'_i}, ...)$  and  $\rightarrow = (\delta_{e_p}, ...)$  such that  $(s_{p'_i}) = \delta_e(s_{p_i}, x)$  where x is an internal event generated by any other process of the system. This transition is enabled before the internal transition that has emitted the event is triggered. However, by construction, we know that it exists  $\delta_{int}(q) = q'$  and  $\emptyset = \lambda(q)$  that corresponds to the transition  $\delta_e(s_{p_i})$ , and ta(q) = 0.

- 3.  $p=(s_{p_i},...), \ p'=(s_{p_i'},...)$  and  $\rightarrow=(\delta_{e_p},...)$  such that  $(s_{p_i'})=\delta_e(s_{p_i},x)$  where x is an external event

received by the system. However, by construction, we know that it exists  $\delta_{ext}(q,x) = q'$  that corresponds to the transition  $\delta_e(s_{p_i}, x)$ .

Thus, A simulates  $P_r$ .

We can then define a DEVS atomic model which simulates exactly the behaviour of a DEv-PROMELA program. It is interesting to note that in the case of a DEv-PROMELA program without global variables and channels, we can build a DEVS coupled model that simulates the DEv-PROMELA specifications. In that case, the property of closure under coupling gives exactly the DEVS atomic model described above, and in this case, the coupled model is similar to the DEv-PROMELA program.

**Proposition 3.** A DEv-PROMELA program  $P_r$  is legitimate if the DEVS equivalent model is legitimate.

Because a DEv-PROMELA program cap be simulated by a DEVS model, we can deduce all the properties of the program from the DEVS model. Particularly, a DEv-PROMELA program is legit mate if the DEVS equivalent model is legitimate. For example, if the DEVS model goes into an infinite loop of interval events where time does not advance beyond a certain point we can deduce that the DEv-PROMELA program has the same behaviour.

### Relation Setween DEv-PROMELA and ROMELA

• Checking a DEv-PROMELA model is possible only if we can at least find an equivalent PROMELA model, meaning the structure expressed by the DEv-PROMELA model can be abstracted to a PROMELA model. We must then prove that it exists at least one PROMELA model which is an abstraction of the given DEv-PROMELA model. We can do that by using the pre-order simulation relationship between models.

**Proposition 4.** Given a DEv-PROMELA process model P, it exists a PROMELA process model P' that preserves the structural properties of P.

Consider a DEv-PROMELA process model P. We get a PROMELA process model P' by removing all the event descriptors and abstracting real data from P. P and P'are two state-transition systems, whose respective entire statespace is denoted S and S'. Thus, P' preserves the structure of P if and only if

$$\forall (s, s') \in S \times S, \exists (t, t') \in S' \times S',$$

$$\delta_i(s) = (s', e) \vee \delta_e(s, e) = s' \Rightarrow t \xrightarrow{l} t'$$

where l is a statement. Look at each type of statement defined previously.

Assignment. A DEv-PROMELA assignment is a statement l with an event descriptor ev that defines one or several transitions between two states s and s'. A PROMELA assignment is a statement l that defines only one transition between two states t and t'. Then, if P' is obtained by removing the event descriptor ev, it exists a  $(t, t') \in S' \times S'$ such that  $t \stackrel{l}{\rightarrow} t'$ .

Selection and repetition constructs. A DEv-PROMELA selection (repetition) construct defines transitions between subsets of S. Given  $S_a \subset S$  and  $S_b \subset S$  such that  $S_a$  verifies a guard, and  $S_b$  is the subset of end states related to the selected option. This means  $\forall s_a \in S_a, \exists s_b \in S_b, \delta_i(s_a) = (s_b, e) \lor \delta_e(s_a) = (s_b, e)$  by executing the option. Then, if P' is obtained by removing the event descriptor, each couple  $(s_a, s_b)$  can be mapped to a  $(t_a, t_b)$  such that  $t_a \stackrel{l}{\rightarrow} t_b$ . Moreover, we can be sure it exists at least one such couple because PROMELA allows non-deterministic behaviours.

Channels. The mechanism of channels is exactly preserved in DEv-PROMELA. Sending and receiving operations link two states s and s'. Only the lifespan and the meaning of transitions are changed. Thus, removing the event descriptor preserves the link between the states.

**Definition 1.** We call autonomous instance of a DEv-PROMELA process P any parametrization of the lifespans of states such that the model contains no passive state.

DEv-PROMELA model allows modelling systems whose next states depend on the time elapsed in the current state. This behaviour can obviously, for example, lead to deadlock in passive state. Because PROMELA does an abstraction of time, these kinds of behaviours cannot be captured or modelled. However, a PROMELA model will be a good abstraction if it covers at least all the parametrizations of the DEv-PROMELA model containing no passive state. In this case, the PROMELA model simulates all the autonomous instances of the DEv-PROMELA model.

**Proposition 5.** Given a DEv-PROMELA process model P and a PROMELA process model P' obtained by remove all the event descriptors. Then, P' simulates all juto somou instances of P.

As demonstrated, P' preserves all the tructural properties of P. The set of autonomous instantes of P contains all the possible orders of events. Because P is a process, only a change in conditional/ op structures can lead to different behaviours between instances. However, the PROMELA model P' contains all the possible paths for these structures. As a consequence, P' signulates all the autonomous instances of P

**Projection 6.** A PROMELA program  $P'_r$  got from a DEV-PROMELA program  $P_r$  by removing all event descriptors preserves the structural properties of  $P_r$ . Moreover,  $P'_r$ simulates all autonomous instances of  $P_r$ .

A global state of a DEv-PROMELA program is the cartesian product of the set of states of each process. Thus, at a time t, the next event (and the next statement) is selected by taking the minimum value of the date of the next event of each process. This means that the statespace represented by all autonomous instances contains all the possible permutations between statements. This is exactly the executing graph of the PROMELA model  $P_r'$ . Then, it exists a PROMELA model that is an abstraction of a DEv-PROMELA model. This model is obtained by only removing the event descriptors from the source model. Moreover, we can say that the symbolic DEv-PROMELA model simulates the PROMELA model.

### 2.6 Nature of DEv-PROMELA

As a consequence of the two relationships presented above, the DEv-PROMELA specifications embbed two representations of timed properties and two points of view of a same transition system. As a DEVS simulation model, the DEv-PROMELA model considers time as quantitative (events are considered as timed events). As a PROMELA verification model, it focuses on time as qualitative (events are considered as ordered events). One important question can be raised from this construction: is DEv-PROMELA an extension of PROMELA? Is DEv-PROMELA a new formalism? Is DEv-PROMELA an extension of DEVS?

DEV-PROMELA is a formalism based on the PROMELA formalism for its syntaxic part, and on DEVS for its semantics. While the syntax defines the macro-level of the underlying automaton, the semantics gives tails o how transition are triggered at the micro-level. This means that the resulting PROMELA model generated from a DEV-PROMELA model is more abstract than the second one, and contains less timed information. Therefore, purely reasonning on a DEV-PROMELA model is possible, and refining a PROMELA model to obtain a DEV-PROMELA model is easily possible by uncating the former model. However, to prove that DEV-PROMELA is an extension of PROMELA we need to prove that any PROMELA models can be encompasted in a DEV-PROMELA model. This demoneration is out of the scope of this paper.

On the other hand, a DEv-PROMELA model is strictly equivalent to a DEVS model as shown previously. This means that there is always a DEVS model which exactly behaves as a DEv-PROMELA model. However, we know that all DEVS models in general cannot be represented by a DEv-PROMELA model, because a DEv-PROMELA model is structurally finite (or at least, it exists a finite symbolic DEVS to represent it, due to the structural equivalence with PROMELA). As a result, we can hypothesize that DEv-PROMELA is a subclass of DEVS [54].

### 2.7 Closure under Coupling

Closure under coupling is an important aspect in hierarchical construction because it ensures that the formalism is well-defined and enables checking for the correctness of coupled models [24, 55]. Basically, closure under coupling gives the assurance that the behaviour of a coupled model can be described by an atomic model, which consequently ensures the validity of the hirarchical construction. Therefore, we have to prove that a DEv-PROMELA model obeys the rules stated in [24] and that a DEv-PROMELA coupled model can be expressed itself as a DEv-PROMELA atomic model.

**Definition 2.** Given a DEv-PROMELA program  $P = (P_0, P_1, ..., P_n, E_p)$  composed by n DEv-PROMELA processes  $P_j = (S_j, E_j, \delta_{i_j}, \delta_{e_j}, s_{0_j}, F_j)$ . We define  $E_p$  as the event set accepted by the network.

**Proposition 7.** We can define a DEv-PROMELA process  $M_p = (S_M, E_p, \delta_{i_M}, \delta_{e_M}, S_{0_M}, F_M)$  which describes the behaviour of P.

In this case:

- $E_p = \cup E_j$ ;

- \$F\_M = \times F\_j\$ for all \$j\$ such as \$P\_j\$ is a component of \$P\$;

\$F\_M = \times F\_j\$ for all \$j\$ such as \$P\_j\$ is a component of \$P\$;

We define then the remaining equivalent function  $\delta_{i_M}$  and  $\delta_{e_M}$ . Given an event  $e \in E_p$  and  $q = (q_0, ..., q_n)$ , we have:

$$\delta_{e_M}(q, e) = (q'_0, ...)$$

with  $q_j' = \delta_{e_j}(q_j, e)$ , and

$$\delta_{i_M}(q) = (\delta_{e_M}^*(q^*, e_j^*), e_j^*)$$

with  $q^*=(q_0,...,\delta^*_{i_j}(q_j),...,q_n)$  and  $e^*_j$  the event resulting from the imminent transition  $\delta^*_{i_j}$ . This transition is unique by definition: if there are concurrent imminent transitions, the priority function selects the next executed transition. The result is that

$$\delta_{e_M}^*(q,e) = (q_0, ..., q_n)$$

if e is the silent event or if there is no component which defines a such partial function for the imminent resulting event e, or

$$\delta_{e_M}^*(q, e) = (..., \delta_{e_j}(q_j, e), ...)$$

if there is a component which defines a partial function for the imminent resulting event e (we recall here that all DEv-PROMELA processes are intercoupled).

By this construction, any DEv-PROMELA program can be rewritten and simulated by a DEv-PROMELA process. However, this construction is possible only because we rigourously define an equivalence between the syntaxic structures in DEv-PROMELA and PROMEL Indeed, transition functions are built on equivalence between the PROMELA state-transition structure and the automaton underlying DEv-PROVELA. The efore, a rigourous demonstration of the losur under coupling should involve a rigourous denot tration of the above construction for each syntaxic structure of PROMELA.

### Werkflow Combined V&

A prodel can be thus used for generating both verification and simulation model. However, it is important to know what exactly the DEv-PROMELA el represents. As an extension of PROMELA, DEv-PROMELA specifications can be a conceptual model of a software, especially event-driven software, or more precisely its formal specifications. While the verification model derived from the specifications removes the computational properties, it can be used for checking the flow and communications between processes. This means that the computerized verification model will be generally used for validating flow properties (what we call static and structural properties). This verification model can also be used for inspecting and verifying the future implementation in a symbolic way. An analogy can be thus done with static test techniques [56].

On the other hand, as a subclass of DEVS, DEv-PROMELA specifications can be considered as a conceptual

model of the computerized simulation model and as a conceptual model of the final software. This model can be used for checking behavioural properties and evaluating data (what we call dynamic and behavioural properties). In particular, it can be used for validating counterexamples given by the model-checker, or confirming the absence of errors by playing scenarios. An analogy can be thus done with dynamic test techniques [56]. Furthermore, while the simulation model is obtained from the DEv-PROMELA specifications model, it means that the verification model is also formal specifications of the simulation model (even the simulator is abstracted). This is important in the case of V&V of simulation models.

Shorter, DEv-PROMELA specifications are formal opecifications and conceptual model of simulators (i.e., the implementation of the simulaton model) and of the final of twait Anyway, depending on what kind of properties is decked simulation and formal verification can be used to both ification or validation purposes. As a formal framework, the DEv-PROMELA specifications can be combined with many traditional techniques for a more rocust ₩ workflow.

### Software Vernication and Validation in 3.2

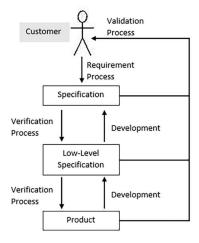

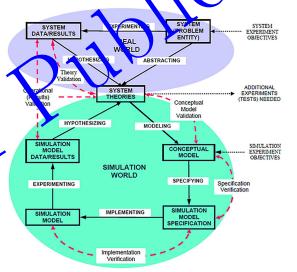

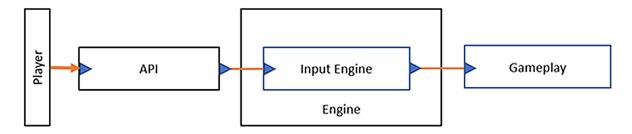

tware Engineering, Software Verification and Validation, and Verification and Validation of Simulation Models roposes many workflows explaining the V&V procedures. The first one (figure 2) shows clearly the difference between verification and validation. Verification processes overcome only during the development phases to check if the computerized program fulfills the development requirements. Validation is the process in which the final user tests the final software and checks if it meets its functional specifications. This means the validation steps are done only on the final software.

Figure 2. Schema of V&V Process from [57].

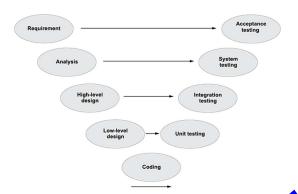

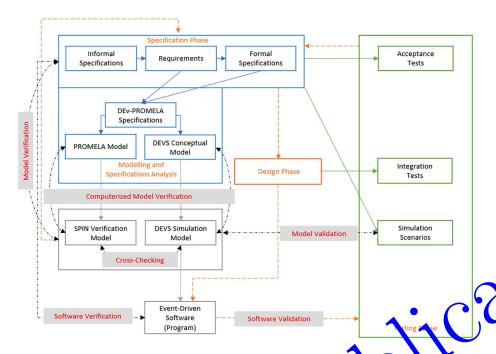

Further, if we precisely look at the development cycle (figure 3), we can see that validation is essentialy testing techniques on the final computer program. At each step of the development cycles corresponds requirements defined at a suitable level of abstraction [58]:

- Unit tests validate each software unit, if they fit for use;

- Integration tests validate each group of combined software unit, if they deliver the expected results;

- System tests (or validation tests) validate the behaviour of the software, in the context of Functional Requirement Specifications and System Requirement Specifications;

- Acceptance tests are formal testing with respect to user needs, requirements, and business processes conducted to determine whether a system satisfies the acceptance criteria and to enable the user, customers or other authorized entity to determine whether or not to accept the system.

Figure 3. V-model representation from [59]

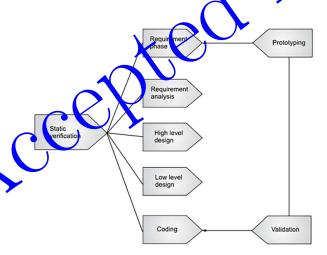

At each intermediate steps, static verification tech ique are also performed (figure 4).

Figure 4. V&V in Software Development Life Cycle proposed by [59].

These techniques evaluate the correctness of the computerized model against the requirements at each step, meaning whether the implementation fulfills the specifications. These techniques essentially concern [60]: code reviews, symbolic execution, data analysis, semantics analysis, etc. As summary, validation a priori concerns only executing the final

software, while verification (or testing) is the fact of checking source code, or a model of this code, at each step of the development cycle.

# 3.3 Verification, Validation and Accreditation of Simulation Models

Verification, Validation and Accreditation of Simulation Models (V&VA) [61] is a specialized V&V procedure applied to simulation models. In fact, simulation models are always developed using observations from an existing system under study or from theoritical assumptions about this system. As a recall, a simulation model is always related to an EF as stated in Section 1. As a consequence, before using a simulation model, ensuring its credibility according to data from real world and from simulation world is necessary. However, a simulation model is also a software program, meaning that Software V&V procedure should also be applied during the development of the simulator.

This feelings is confirmed when we analyze he V&V workflow of simulation models (figure 5).

Figure 5. The Sargent Circle for V&V of Simulation Model [2].

In this one, we can clearly see that verification procedures concern only the computerized simulation model and the simulation model specifications. Validation then consists on using a set of test data to ensure the simulator replicates the real system. However, in the same manner than dynamic verification blurs the boundary between verification and validation, we can see that simulation model is indirectly used for validating the conceptual model. Indeed, the simulation model allows inferring new hypothesis on the system theories which is used for building the conceptual model. This means that, if simulation is used on a model of software, it can be used for both verification and validation purposes. In the same manner, while verification is the fact of checking the correctness of an implementation against specifications, model-checking can be used for validating behaviours using an abstraction of a software. This means that model-checking is also a validation activity [62, 63], even if it is performed not on the software itself, but on a model of it.

These notions are very important while designers must exactly know what they are working on. Moreover, DEV-PROMELA adds a new level in the development cycle. For these reasons, we develop a clearer iterative V&V workflow.

### 3.4 Workflow with Combined V&V