## Impact of Total Ionizing Dose on the alpha-Soft Error Rate in FDSOI 28 nm SRAMs

Soilihi Moindjie, Daniela Munteanu, Jean-Luc Autran, Victor Malherbe,

Gilles Gasiot, Philippe Roche

### ► To cite this version:

Soilihi Moindjie, Daniela Munteanu, Jean-Luc Autran, Victor Malherbe, Gilles Gasiot, et al.. Impact of Total Ionizing Dose on the alpha-Soft Error Rate in FDSOI 28 nm SRAMs. Microelectronics Reliability, 2023, pp.115181. 10.1016/j.microrel.2023.115181. hal-04194288

## HAL Id: hal-04194288 https://amu.hal.science/hal-04194288

Submitted on 2 Sep 2023

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# Impact of Total Ionizing Dose on the alpha-Soft Error Rate in FDSOI 28 nm SRAMs

S. Moindjie<sup>a</sup>, D. Munteanu<sup>a</sup>, J.L. Autran<sup>a,\*</sup>, V. Malherbe<sup>b</sup>, G. Gasiot<sup>b</sup>, P. Roche<sup>b</sup>

<sup>a</sup>Aix-Marseille Univ., CNRS, IM2NP (UMR 7334), 13397 Marseille Cedex 20, France <sup>b</sup>STMicroelectronics, 850 rue Jean Monnet, 38926 Crolles Cedex, France

Abstract – Synergy effect of total ionizing dose (TID) on alpha-soft error rate ( $\alpha$ -SER) in FDSOI 28nm SRAM has been experimentally characterized using a dedicated setup combining alpha-particle irradiation (<sup>241</sup>Am solid source) in vacuum chamber and 10 keV X-ray irradiation. Measurements have been performed on a 3 Mbit singleport SRAM cut powered at 1V. Irradiations up to 125 krad(Si) have been achieved and their impact on the  $\alpha$ -SER has been characterized from the cumulated number of bitflips as a function of the exposition time to the alphasource. Modelling and simulation have been used to link transistor threshold voltage variations to SRAM cell stability in terms of static noise margin (SNM), critical charge ( $Q_{crit}$ ) and finally estimated SER, in good agreement with experimental results.

#### Keywords

Total ionizing dose, X-ray irradiation, soft error rate, synergy effects, alpha particle, single-event upset, fully-depleted silicon-on-insulator, SRAM memory, static noise margin, critical charge, modelling, numerical simulation

#### Highlights

- Synergy effect of total ionizing dose on alpha-soft error rate in SRAM has been characterized

- Results concern 3 Mbit single-port SRAM powered at 1V in FDSOI 28nm technology

- X-ray irradiation up to 125 krad(Si) have been combined with SER measurements using a <sup>241</sup>Am source

- SER degradation is linked to SRAM static noise margin reduction that induces critical charge decrease

- 15% reduction of the critical charge at 125 krad(Si) results in doubling the alpha-soft error rate

#### \* Corresponding author:

Prof. Jean-Luc Autran, Aix-Marseille Univ., CNRS, IM2NP - UMR CNRS 7334, Faculté des Sciences – Service 142, Avenue Escadrille Normandie – F-13397 Marseille Cedex 20 France – Phone: + 33 (0)413 594 627 – Email: jean-luc.autran@univ-amu.fr

#### 1. Introduction

Total ionizing dose (TID) is known to enhance the susceptibility of circuits to single-event effects (SEE) by modifying the electrical characteristics of individual transistors inside the exposed circuit [1-15]. In the case of static random-access memories (SRAMs), the radiation-induced defects and trapped charges, mainly in oxide and dielectric layers and at their interfaces with the semiconductor, alter the electrical conditions within the SRAM cells, affecting transistor threshold voltages and consequently SRAM stability. The degradation of this latter results in a reduction of the static noise margin (SNM) – the minimum noise voltage present at each of the cell storage nodes necessary to flip the state of the cell – and, consequently, in the reduction of the critical charge ( $Q_{crit}$ ) – the minimum charge deposited by a ionizing particle at one of the nodes necessary to flip the state of the cell [16-17] – of the SRAM circuit, as shown in some previous studies [8-15].

These synergy effects between TID and single-event effects in devices and circuits are fundamental to apprehend electronic reliability in various environments, like space, accelerators, or future power fusion reactors. In such complex radiation environments, equipment or payloads are or will be subjected to both TID and SEE at the same time, which leads to combined effects on the electronics. However, radiation qualification procedures often perform separate characterizations and, consequently, are not able to catch the underlying physical mechanisms responsible of dose-enhancement SEE sensitivity or other effects [11].

In this work, we experimentally investigate synergy effects between TID and alpha-particle SER in FDSOI 28nm SRAM combining the use of a <sup>241</sup>Am solid source and 10 keV X-ray irradiation machine to successively degrade and evaluate the circuit response. The key objective of this study is to model and simulate such effects, step by step, from individual transistor threshold voltage variations to SRAM SER, evaluating the cell stability in terms of static noise margin, critical charge, and finally soft error rate. The paper is organized in two main parts: we describe in Section 2 the circuit under test and the irradiation test setups and procedures, as well as the experimental results. In Section 3, modelling and simulation aspects are presented and used to reproduce experimental data.

#### 2. Experiments

#### 2.1. SRAM test vehicle

In this study, we used a dedicated test vehicle (ANYA\_D) manufactured by STMicroelectronics using a commercial ultra-thin body and buried oxide (UTBB) fully-depleted silicon-on-insulator (FDSOI) CMOS 28 nm technology. The UTBB-FDSOI uses a 28 nm high-κ metal-gate, the silicon layer is 7 nm thick on top of an ultra-

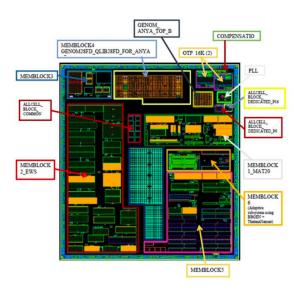

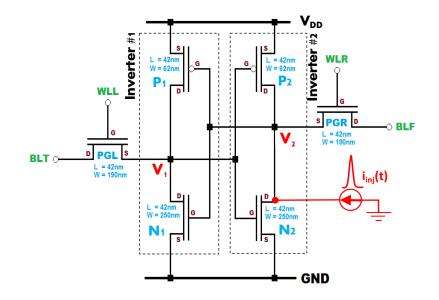

thin buried oxide of 25 nm. Details can be found in [18-20], including process description, electrical performances and single event test results for the terrestrial radiation environment (alphas and neutrons). ANYA\_D embeds several SRAMs cuts of various densities and power features (Fig. 1). For the purposes of the study, we performed all our measurements on a 3 Mbit single-port high-density (SPHD) SRAM cut powered at  $V_{DD} = 1$  V. The circuit schematic of the corresponding SPHD SRAM cell with transistor layout dimensions is given in Fig. 2.

Figure 1. GDS view of ANYA\_D test vehicle.

Figure 2. Circuit schematic of the single-port high-density (SPHD) SRAM cell.

#### 2.2. Experimental setups

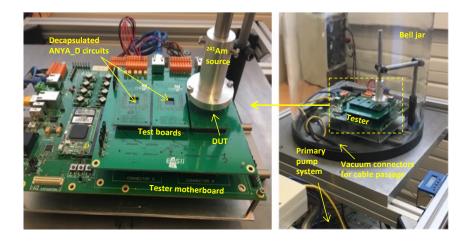

For the purpose of the study of synergy effects, we designed, constructed and operated a complete experimental setup for both  $\alpha$ -SER and TID measurements. This setup consists of a vacuum chamber (bell jar) in which a circuit tester can be operated under a primary vacuum (10<sup>-2</sup> mbar), in order to maintain the energy of alpha-particles emitted by the source at the level of the entry face of the circuit. The circuit test is a custom tester developed by EASII-IC composed of a main motherboard and one or several test boards. The design of both the hardware and software components of the system follows all the specifications of the JEDEC SER test standard [16]. Each ANYA D device under test (DUT) is soldered on a DUT test board directly connected to the motherboard. No other active device is present on the test board excepting the tested DUT. The motherboard itself is based on a Xilinx Virtex5 FPGA with embedded memory and a PXA270 processor with Ethernet TCP/IP stack protocol connection. The tester embeds an internal soft error scrubbing code in order to detect internal soft errors. This tester is fully connected to the exterior via vacuum connectors. A power supply with a remote voltage sensing probe is connected to the mother board, as close as possible to the devices. It allows the monitoring of the current consumption of the devices. The measurements are performed independently per power supply line. Fig. 3 shows the experimental setup in irradiation configuration with an <sup>241</sup>Am solid source placed in front of a single decapsulated ANYA D circuit, ready to characterize. Setup of Fig. 3 was used to perform tthe  $\alpha$ -SER characterization of the circuit under test. After exposing the DUT to the alpha source and initializing the SRAM memory plan with a checkerboard test pattern, the tester searches for errors in loop in the SRAM array until the test sequence is terminated.

**Figure 3.** Alpha-particle irradiation setup using a  $^{214}$ Am solid source (4 kBq in  $2\pi$  sr) and a vacuum bell jar. All circuit connections go through vacuum connectors, allowing real-time measurements during irradiation.

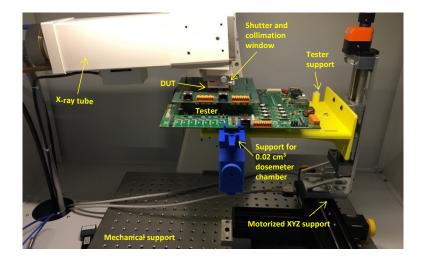

After this measurement step, the tester itself with the circuit was moved to the X-ray irradiation setup (Fig. 4) for irradiation at a dose rate of 100 rad(Si)/s. During X-ray irradiation, the SRAM memory plan was maintained initialized with the same checkerboard test pattern as used during  $\alpha$ -irradiation.

Repeating the cycle ( $\alpha$ -SER measurement + X-ray irradiation) for different values of the TID allows us to characterize synergy effects between SER and TID from 0 to 128 krad(Si).

**Figure 4.** X-ray irradiation setup using a 10 keV X-ray tube with a tungsten cathode (for clarity, the circuit tester is not connected).

#### 2.3. $\alpha$ -SER versus TID experimental results

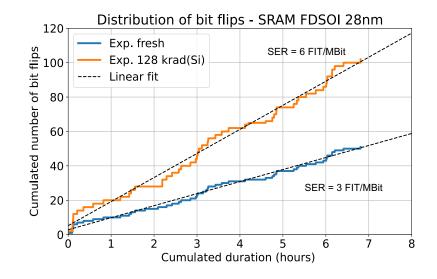

Figure 5 shows the cumulated number of bit flips detected during  $\alpha$ -irradiation as a function of measurement time before (fresh) and after X-ray irradiation that corresponds to the maximum dose of 128 krad(Si) for which the circuit is fully functional. Note the surprisingly long duration of the experiments (up to 7 hours) for such accelerated tests using a source with 4 kBq of activity: this is due to the relative immunity of FDSOI architectures to single events, characterized by very low SER values [19-20], reported in Fig. 5. In this sense, the curves of Fig. 5 resemble those of real-time SER experiments, but with a different abscissa, expressed in hours and not in months or years of exposure to radiation [21-23]. The two distribution slopes of Fig. 5 are directly linked to the  $\alpha$ -SER: after 128 krad(Si), the slope (and thus the SER) is quasi twice that of the distribution before irradiation, demonstrating the TID synergy effect on the circuit SER. It must be noted at this level that the magnitude of the SER degradation may depend on the test patterns applied during TID and alpha-particle irradiation sequences [24] but this effect is out of the scope of our study. In the following, our objective is to step-by-step retrieve by simulation and confirm this measured SER from the TID response of both NMOS and PMOS transistors, elements of the SRAM cell.

**Figure 5.** Cumulated number of bit flips in 3 Mbit SRAM cut ( $V_{CC} = 1 V$ ) as a function of the  $\alpha$ -irradiation time before (fresh) and after 128 krad(Si) X-ray irradiation of the circuit. The corresponding SER (FIT/Mbit) is calculated for an  $\alpha$ -emissivity of 10<sup>-3</sup>  $\alpha$ /cm<sup>2</sup>/h. For industrial confidentiality reason, all SER results have been normalized by a common arbitrary scaling factor.

#### 2.4. TID characterization of individual transistors

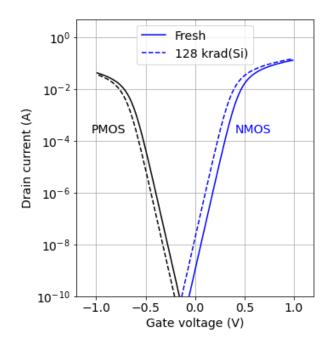

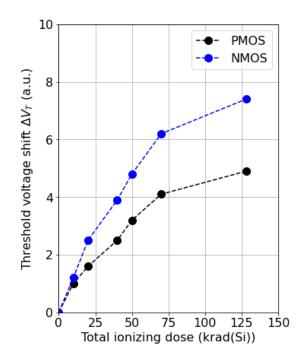

In complement to SER versus TID experiments, we performed electrical characterization of individual transistors for the extraction of the threshold voltage shift as a function of TID. Figure 6 shows the  $I_D(V_G)$  characteristics before irradiation and after 128 krad(Si) for both NMOS and PMOS individual transistors.  $\Delta V_T$  is negative since the radiation-induced trapped charges are mainly positive whatever the type of the transistor [7].  $\Delta V_T$  versus TID (Fig. 7) are also more important in absolute value for NMOS than for PMOS. The latter appear to be less TID-sensitive than NMOS, as already shown [25].

Figure 6.  $I_D(V_G)$  characteristics before (fresh) and after 10 keV X-ray irradiation at 128 krad(Si) for both NMOS and PMOS transistors (L = 42 nm, W = 1  $\mu$ m).

Figure 7. Negative threshold voltage shifts versus TID extracted from  $I_D(V_G)$  curves for both NMOS and PMOS transistors. For industrial confidentiality reason, all values have been normalized by a common arbitrary scaling factor.

#### 3. Modelling and simulation

#### 3.1 Transistor and SRAM modelling

We implemented in C++ the UTSOI model (v1.1.4) developed by the CEA-LETI (and initially in the form of Verilog-A(MS) source code) for ultra-thin fully depleted SOI MOSFET [26]. This surface potential model was implemented under the form of two numerical functions  $I_{DN}(V_G, V_D)$  and  $I_{DP}(V_G, V_D)$  returning the source-to-drain current for NMOS and PMOS transistors, respectively, with  $V_G$  and  $V_D$  the applied voltages on the gate and drain terminals, respectively (here  $V_S = V_B = 0$  V for source and bulk terminals). In this model, the source-to-drain current expression is obtained by a similar equation as in PSP model [27]:

$$I_{D} = WC_{ox} \mu \frac{kT}{q} \left[ \int_{x_{n,s}}^{x_{n,d}} q_{i} dx_{n} - \int_{q_{i,s}}^{q_{i,d}} dq_{i} \right]$$

(1)

where  $C_{ox}$  is the gate oxide capacitance per unit area,  $q_i$  is the inversion charge,  $\mu$  is the carrier mobility, W is the channel width,  $x_{n,d}$  and  $x_{n,s}$  are the quasi Fermi levels at the drain and source sides respectively,  $q_{i,d}$  and  $q_{i,s}$  are the inversion charges at the drain and source sides, respectively.

Note that the integral terms in Eq. (1) depend, among other parameters, on the channel length L and on the transistor threshold voltage  $V_T$ , that do not explicitly appear in this formulation. Eq. (1) can be expressed analytically considering a series of developments and approximations described in [28]. It has been used in our standalone SRAM cell simulator [29-30] for time-domain transient simulation and for the determination of the static noise margin (SNM) and critical charge Q<sub>crit</sub>, as explained in the following. Considering the storage node of the SRAM cell of Fig. 2 composed of the two cross-coupled inverters #1 and #2, the time variations of the node voltages  $V_1$  and  $V_2$  are solutions of the system of two coupled differential equations:

$$\begin{cases} \frac{dV_1}{dt} = \frac{I_{DP1}(V_2 - V_{DD}, V_1 - V_{DD}) - I_{DN1}(V_2, V_1)}{C_N} = F(t, V_1, V_2) \\ \frac{dV_2}{dt} = \frac{-i_{inj}(t) + I_{DP2}(V_1 - V_{DD}, V_2 - V_{DD}) - I_{DN2}(V_1, V_2)}{C_N} = G(t, V_1, V_2) \end{cases}$$

(2)

where index 1 and 2 refer to the two inverters of the SRAM cell (defined in Fig. 2),  $C_N$  is the storage node capacitance (determined from technological process and layout proprietary information),  $i_{inj}(t) = 0$  for the determination of the static noise margin of the SRAM cell and  $i_{inj}(t)$  is given by Eq. (8) (see section 3.3.)

This system of differential equations can be easily solved in the time domain, using a 4<sup>th</sup> order Runge-Kutta method [31] with a time step  $\Delta t$ . Using notations introduced in Eq. (2), the incremental results for  $t_{n+1} = t_n + \Delta t$  are:

$$\begin{cases} V_1^{n+1} = V_1^n + \frac{K_1 + 2K_2 + 2K_3 + K_4}{6} \\ V_2^{n+1} = V_2^n + \frac{L_1 + 2L_2 + 2L_3 + L_4}{6} \end{cases}$$

(3)

with:

$$K_1 = F(t^n, V_1^n, V_2^n) \Delta t \quad L_1 = G(t^n, V_1^n, V_2^n) \Delta t$$

(4)

$$K_{2} = F(t^{n} + \frac{\Delta t}{2}, V_{1}^{n} + \frac{K_{1}}{2}, V_{2}^{n} + \frac{L_{1}}{2})\Delta t \quad L_{2} = G(\dots)\Delta t$$

(5)

$$K_3 = F(t^n + \frac{\Delta t}{2}, V_1^n + \frac{K_2}{2}, V_2^n + \frac{L_2}{2})\Delta t \quad L_3 = G(\ldots)\Delta t$$

(6)

$$K_4 = F(t^n + \frac{\Delta t}{2}, V_1^n + K_3, V_2^n + L_3)\Delta t \quad L_4 = G(\ldots)\Delta t$$

(7)

where the argument for G in the second member of these equations is the same as for F.

Equations (3) to (7) constitute the core model for solving the time evolution of the SRAM cell node voltages. For the static noise margin determination, each differential equation of (2) can be solved separately, imposing a voltage sweep from 0 to V<sub>DD</sub> for the voltage of the second node.

#### 3.2. Static noise margin

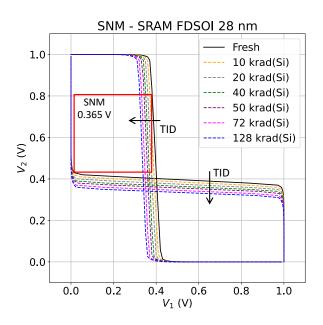

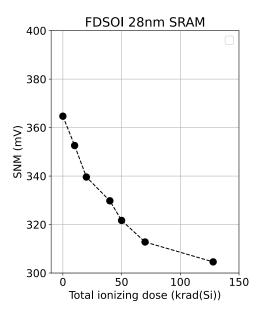

Figure 8 shows the computed SRAM "butterfly" curves before and after several doses, up to 128 krad(Si). The effect of the dose on the reduction of the static noise margin, taken into account via the  $\Delta V_T$  values for both PMOS and NMOS transistors of the SRAM cell, is clearly visible. For memory, the SNM is defined as the side length of the largest square that can be fitted inside the lobes of the "butterfly" curve. Figure 8 evidences the closing of the curves, quantified in Fig. 9 in terms of SNM values. At 128 krad(Si), SNM is reduced to about 20% with respect to the value before irradiation.

**Figure 8.** Simulated SRAM cell "butterfly" curves before and after irradiation at several TID values. SNM is graphically extracted here for the curve before irradiation (fresh).

**Figure 9.** SNM versus TID for the FDSOI 28 nm SPHD SRAM cell defined in Fig. 2 and extracted from numerical simulation shown in Fig. 8.

#### 3.3. Critical charge

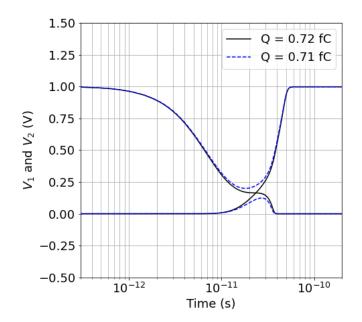

The decrease in stability of the SRAM cell, evidenced by the SNM reduction, has a direct impact on its susceptibility to single events. For simulating such events at circuit level, we solve this time the full system of equations (2) considering the variations of the transistor threshold voltages in both I<sub>DN</sub> and I<sub>DP</sub> calculation functions and a double exponential current transient pulse  $i_{inj}(t)$  injected on the struck node #2 (see Fig. 2) during the transient simulation [32]:

$$i_{inj}(t) = \frac{Q}{t_f - t_r} [exp(-t/t_f) - exp(-t/t_r)]$$

(8)

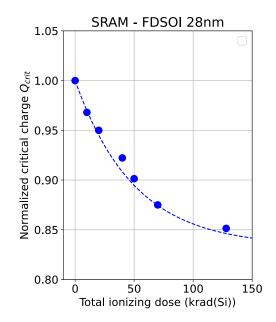

where Q is the collected charge on the struck node (i.e., the integral of the pulse),  $t_r$  is the rising time constant, and  $t_f$  is the falling time constant. Slowly varying Q around the stability point of the SRAM cell allows us to determine the critical charge for a given TID value, as illustrated in Fig. 10 for the fresh cell. Figure 11 shows the decrease of Q<sub>crit</sub> with TID, as deduced from the above circuit simulation. The normalized Q<sub>crit</sub>(D)/Q<sub>crit</sub>(0) variation with the total ionizing dose D (expressed in krad(Si)) is empirically well described by an exponential law under the form:

$$Q_{crit}(D)/Q_{crit}(0) = A + B \times exp(-\lambda D)$$

(9)

where parameters A = 0.83 (unitless), B = 0.167 (unitless) and  $\lambda = 0.02 \text{ krad}(\text{Si})^{-1}$ .

Figure 10. Transient simulation of the SRAM cell (before irradiation) subjected to a particle strike mimicked by (8) with two values of Q.  $V_1$  and  $V_2$  correspond to the potentials of the two storage nodes of the cell.

**Figure 11.** Critical charge versus TID extracted from transient simulation considering a double exponential current pulse.

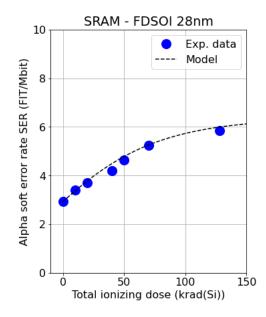

#### 3.4. Soft error rate

The decrease of  $Q_{erit}$  versus TID highlighted in Fig. 11 logically leads to an increase of the SER with TID, as evidenced in Fig. 12. In this figure, experimental SER data have been obtained from the cumulated distributions of bit flips as a function of the  $\alpha$ -irradiation time (see Fig. 5) for the different TID values (remember that the extracted SER values expressed in FIT/Mbit are calculated for an  $\alpha$ -emissivity of 10<sup>-3</sup>  $\alpha$ /cm<sup>2</sup>/h). Experimental results show that the SER is multiplied by a factor of two by a total ionized dose of 125 krad(Si). This evolution of the SER values with TID is not linear and can be nicely described with the Hazucha and Svensson's equation for the SER [33]:

$$SER = K \times exp(-Q_{crit}/Q_S) \tag{10}$$

where the prefactor K and the collection efficiency  $Q_S$  are two fitting parameters and  $Q_{crit}$  values correspond to data of Fig. 11.

**Figure 12.** Alpha soft error rate versus TID for the FDSOI 28 nm SPHD SRAM as deduced from experimental data of Fig. 5 and from Eq. (10) using Q<sub>crit</sub> values of Fig. 11.

The best fit of Eq. (10) on SER data is obtained with K = 310 FIT/Mbit and  $Q_s = 0.154$  fC, as illustrated in Fig. 12. The behavioural modelling predicted by this equation is an important quantitative information that can be imported in design for reliability tools used to size electronic systems containing the characterized memory for a given mission profiles, for example for space applications.

#### 4. Conclusion

In conclusion, we investigated the synergy effect of total ionizing dose on alpha-soft error rate paper in a 3 Mbit SRAM test circuit manufactured by STMicroelectronics in CMOS 28nm FDSOI technology. This work is original for this technology and self-consistent in so far as it clearly details the methodology and gives all the equations, models and calculation steps to relate the performance of individual transistors to the response of the SRAM cell, from an electrical stability and soft-error rate points of view. Synergy effects were experimentally characterized using a circuit tester alternatively embedded in vacuum chamber for alpha-particle irradiation using a <sup>241</sup>Am solid source and in an irradiation machine for 10 keV X-ray exposure. Total ionizing doses up to 125 krad(Si) have been performed and their impact on the  $\alpha$ -SER has been characterized from the cumulated number of bitflips as a function of the exposition time to the alpha-source detected on a 3 Mbit single-port SRAM cut powered at 1V. Our experimental result showed that a 15% reduction of the critical charge at 125 krad(Si) results in doubling the alpha-soft error rate from 3 to 6 FIT/Mbit. Modelling and simulation of the storage element (double inverter) of a single SRAM cell was conducted, considering a dedicated and characterized FDSOI transistor model (UTSOI v.1.1.4) and a double exponential current transient pulse to emulate the impact of alpha-particles on the SRAM sensitive node. Simulation results quantitively link transistor threshold voltage variations to SRAM cell stability in terms of static noise margin and critical charge. The estimated reduction of the soft error rate was found in excellent agreement with experimental results, demonstrating that such a behavioural modelling can be used for reliability prediction of this FDSOI SRAM technology, considering a given mission profiles combining TID and single event constraints, for example for space applications.

#### Acknowledgements

The financial support of the French DGA directorate (DGA/RAPID #162906056) is gratefully acknowledged. The authors also thank M. Naceur and the technical staff of EASII-IC (Grenoble) for the development of electronic cards and testers.

#### References

- A.R. Knudson, A.B. Campbell and E.C. Hammond, "Dose Dependence of Single Event Upset Rate in MOS dRAMS," *IEEE Transactions on Nuclear Science*, vol. 30, no. 6, pp. 4508-4513, Dec. 1983.

- [2] A.B. Campbell and W.J. Stapor, "The Total Dose Dependence of the Single Event Upset Sensitivity of IDT Static RAMs," *IEEE Transactions on Nuclear Science*, vol. 31, no. 6, pp. 1175-1177, Dec. 1984.

- [3] C.L. Axness, J.R. Schwank, P.S. Winokur, J.S. Browning, R. Koga and D.M. Fleetwood, "Single event upset in irradiated 16 K CMOS SRAMs," *IEEE Transactions on Nuclear Science*, vol. 35, no. 6, pp. 1602-1607, Dec. 1988.

- [4] E.G. Stassinopoulos, G.J. Brucker, O. Van Gunten and H.S. Kim, "Variation in SEU sensitivity of doseimprinted CMOS SRAMs," *IEEE Transactions on Nuclear Science*, vol. 36, no. 6, pp. 2330-2338, Dec. 1989.

- [5] K. Hirose et al., "Total-dose and single-event-upset (SEU) resistance in advanced SRAMs fabricated on SOI using 0.2 μm design rules," 2001 IEEE Radiation Effects Data Workshop. NSREC 2001. Workshop Record. Held in conjunction with IEEE Nuclear and Space Radiation Effects Conference (Cat. No.01TH8588), Vancouver, BC, Canada, 2001, pp. 48-50.

- [6] L.S. Erhardt, D.S. Haslip, T. Cousins, R. Buhr and D. Estan, "Gamma enhancement of proton-induced SEE cross section in a CMOS SRAM," *IEEE Transactions on Nuclear Science*, vol. 49, no. 6, pp. 2984-2989, Dec. 2002.

- [7] M. Hartwell, C. Hafer, P. Milliken and T. Farris, "Megarad total ionizing dose and single event effects test results of a radhard-by-design 0.25 micron ASIC [space applications]," 2004 IEEE Radiation Effects Data Workshop (IEEE Cat. No.04TH8774), Atlanta, GA, USA, 2004, pp. 104-109.

- [8] J.R. Schwank et al., "Effects of Total Dose Irradiation on Single-Event Upset Hardness," IEEE Transactions on Nuclear Science, vol. 53, no. 4, pp. 1772-1778, Aug. 2006.

- [9] R. Koga, P. Yu, K. Crawford, J. George and M. Zakrzewski, "Synergistic Effects of Total Ionizing Dose on SEU Sensitive SRAMs," 2009 IEEE Radiation Effects Data Workshop, Quebec, QC, Canada, 2009, pp. 127-132,

- [10] E.C.F. Pereira, O.L. Gonçalez, R.G. Vaz, C.A. Federico, T.H. Both and G.I. Wirth, "The effects of total ionizing dose on the neutron SEU cross section of a 130 nm 4 Mb SRAM memory," 15<sup>th</sup> Latin American Test Workshop - LATW, Fortaleza, Brazil, pp. 1-4, 2014

- [11] L. Salvy et al., "Total ionizing dose influence on the single event effect sensitivity of active EEE components," 16<sup>th</sup> European Conference on Radiation and Its Effects on Components and Systems (RADECS), Bremen, Germany, 2016.

- [12] Q. Zheng et al., "Total Ionizing Dose Influence on the Single-Event Upset Sensitivity of 130-nm PD SOI SRAMs," *IEEE Transactions on Nuclear Science*, vol. 64, no. 7, pp. 1897-1904, July 2017.

- [13] Q. Zheng et al., "The Increased Single-Event Upset Sensitivity of 65-nm DICE SRAM Induced by Total

Ionizing Dose," IEEE Transactions on Nuclear Science, vol. 65, no. 8, pp. 1920-1927, Aug. 2018.

- [14] Y. Luo, F. Zhang, X. Pan, H. Guo and Y. Wang, "Impact of Total Ionizing Dose on Low Energy Proton Single Event Upsets in Nanometer SRAM," *IEEE Transactions on Nuclear Science*, vol. 66, no. 7, pp. 1848-1853, July 2019.

- [15] J. Li *et al.*, "Effects of total ionizing dose on transient ionizing radiation upset sensitivity of 40–180 nm SRAMs", *AIP Advances* 12, 015026 (2022).

- [16] JEDEC Standard, "Measurement and Reporting of Alpha Particle and Terrestrial Cosmic Ray-Induced Soft Errors in Semiconductor Devices," N° JESD89B, Revision of JESD89A, Sept. 2021.

- [17] D. Munteanu and J.L. Autran, "Modeling and Simulation of Single-Event Effects in Digital Devices and ICs," *IEEE Transactions on Nuclear Science*, vol. 55, no. 4, pp. 1854-1878, Aug. 2008.

- [18] N. Planes, et al., "28nm FDSOI Technology Platform for High-Speed Low-Voltage Digital Applications,"

p. 333, VLSI, 2012.

- [19] P. Roche, J.L. Autran, G. Gasiot and D. Munteanu, "Technology Downscaling Worsening Radiation Effects in Bulk: SOI to the Rescue," *IEEE International Electron Devices Meeting (IEDM)*, pp. 31.1.1 - 31.1.4, Dec. 2013.

- [20] G. Gasiot *et al.*, "SER/SEL performances of SRAMs in UTBB FDSOI28 and comparisons with PDSOI and BULK counterparts," *IEEE International Reliability Physics Symposium*, Waikoloa, HI, USA, pp. SE.6.1-SE.6.5, 2014.

- [21] J.L. Autran, D. Munteanu, G. Gasiot and P. Roche, "Real-time soft-error rate measurements: A review", *Microelectronics Reliability*, vol. 54, pp. 1455-1476, 2014.

- [22] S. Moindjie, J.L. Autran, D. Munteanu, G. Gasiot and P. Roche, "Multi-Poisson process analysis of realtime soft-error rate measurements in bulk 65 nm and 40 nm SRAMs," *Microelectronics Reliability*, vol. 76-77, pp. 53-57, 2017.

- [23] J.L. Autran *et al.*, "Soft-errors induced by terrestrial neutrons and natural alpha-particle emitters in advanced memory circuits at ground level", *Microelectronics Reliability*, vol. 50, pp. 1822–1831, 2010.

- [24] R. Koga, P. Yu, K. Crawford, J. George and M. Zakrzewski, "Synergistic Effects of Total Ionizing Dose on SEU Sensitive SRAMs," 2009 IEEE Radiation Effects Data Workshop, Quebec, QC, Canada, pp. 127-132, 2009.

- [25] M. Gaillardin et al., "Total Ionizing Dose Effects Mitigation Strategy for Nanoscaled FDSOI Technologies," *IEEE Transactions on Nuclear Science*, vol. 61, no. 6, pp. 3023-3029, Dec. 2014.

- [26] https://www.leti-cea.fr/cea-tech/leti/Documents/UTSOI/Model Description UTSOI v113 light.pdf

- [27] R. Langevelde and G. Gildenblat, "PSP: An advanced surface-potential-based MOSFET model" in *Transistor level modelling for analog/RF IC design*, edited by W. Grabinski, B. Nauwelaers, D. Schreurs. Dordrecht: Springer, 2006.

- [28] T.L. Chen and G. Gildenblat, "Analytical approximation for the MOSFET surface potential," *Solid-State Electronics*, vol. 45, no. 2, pp. 335-339, 2001.

- [29] J.L. Autran et al., "Charge Collection Physical Modeling for Soft Error Rate Computational Simulation in Digital Circuits," in *Modeling and Simulation in Engineering Sciences*, N. Sher Akbar, O. Anwar Beg. (Edts.), IntechOpen, pp.115-137, 2016.

- [30] M. Glorieux, J.L. Autran, D. Munteanu, S. Clerc, G. Gasiot, and P. Roche, "Random-Walk Drift-Diffusion Charge-Collection Model for Reverse-Biased Junctions Embedded in Circuits," *IEEE Transactions on Nuclear Science*, vol. 61, no. 6, pp. 3527-3534, Dec. 2014.

- [31] J.C. Butcher, Numerical Methods for Ordinary Differential Equations, 2<sup>nd</sup> edition. Hoboken: Wiley-Blackwell, 2008.

- [32] J.L. Autran and D. Munteanu. Soft errors: from particles to circuits. Boca Raton: CRC Press, 2015.

- [33] P. Hazucha and C. Svensson, "Impact of CMOS Technology Scaling on the Atmospheric Neutron Soft Error Rate," *IEEE Transactions on Nuclear Science*, vol. 47, no. 6, pp. 2586-2594, Dec. 2000.